## Public

# Infineon Technologies AG Chipcard & Security

**Evaluation Documentation**

## SLE88CNFX6600PM / m8864

## **Security Target**

Version 0.3 Date 2011-05-30 Author Jürgen Noller

Print Date:6/17/2011 9:16:00 AMFilename:SLE88CNFX6600PM\_SecTar.doc

**Ú**2011 Infineon Technologies AG. All rights reserved. This document and all information contained therein is considered proprietary of Infineon technologies AG. Infineon technologies AG reserves the right to change the specification or parts of it without prior notice.

### **REVISION HISTORY**

| 0.1 | 2010-12-20: Initial Version           |

|-----|---------------------------------------|

| 0.2 | 2011-02-25: Modification of FCS_COP.1 |

| 0.3 | 2011-05-30: Final Version             |

|  |  | Date: 2011-05-30 | Page: 2/59 |

|--|--|------------------|------------|

|--|--|------------------|------------|

## TABLE OF CONTENTS

| 1 | SECURITY TARGET INTRODUCTION (ASE_INT)                                                                                                        | 6   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | <ul> <li>1.1 SECURITY TARGET AND TARGET OF EVALUATION REFERENCE</li></ul>                                                                     |     |

| 2 | TARGET OF EVALUATION DESCRIPTION                                                                                                              |     |

| 2 |                                                                                                                                               |     |

|   | <ul><li>2.1 TOE DEFINITION</li><li>2.2 SCOPE OF THE TOE</li></ul>                                                                             |     |

|   | 2.2.1 Hardware of the TOE                                                                                                                     | .13 |

|   | 2.2.2 Firmware and software of the TOE                                                                                                        |     |

|   | <ul> <li>2.2.3 Interfaces of the TOE</li> <li>2.2.4 Guidance documentation</li> </ul>                                                         |     |

|   | 2.2.5 Forms of delivery                                                                                                                       |     |

|   | 2.2.6 Production sites                                                                                                                        |     |

|   | 2.2.7 Availability of functionality                                                                                                           |     |

| 3 | CONFORMANCE CLAIMS (ASE_CCL)                                                                                                                  | .18 |

|   | 3.1 CC CONFORMANCE CLAIM                                                                                                                      |     |

|   | 3.2         PP CLAIM           3.3         PACKAGE CLAIM                                                                                      |     |

|   | 3.4 CONFORMANCE RATIONALE                                                                                                                     |     |

| 4 | SECURITY PROBLEM DEFINITION (ASE_SPD)                                                                                                         | .21 |

|   | 4.1 THREATS                                                                                                                                   | .21 |

|   | 4.1.1 Additional Threat due to TOE specific Functionality                                                                                     | .21 |

|   | <ul><li>4.1.2 Assets regarding the Threats</li><li>4.2 ORGANIZATIONAL SECURITY POLICIES</li></ul>                                             |     |

|   | 4.2.1 Augmented Organizational Security Policy                                                                                                |     |

|   | 4.3 ASSUMPTIONS                                                                                                                               | .23 |

|   | 4.3.1 Augmented Assumptions                                                                                                                   |     |

| 5 | SECURITY OBJECTIVES (ASE_OBJ)                                                                                                                 |     |

|   | 5.1 SECURITY OBJECTIVES FOR THE TOE.                                                                                                          |     |

|   | 5.2 SECURITY OBJECTIVES FOR THE DEVELOPMENT AND OPERATIONAL ENVIRONMENT<br>5.2.1 Clarification of "Usage of Hardware Platform (OE.Plat-Appl)" |     |

|   | 5.2.2 Clarification of "Treatment of User Data (OE.Resp-Appl)"                                                                                | .27 |

|   | 5.2.3 Clarification of "Protection during Composite product manufacturing (OE.Process-Sec-IC)"                                                |     |

| _ | 5.3 SECURITY OBJECTIVES RATIONALE                                                                                                             |     |

| 6 | EXTENDED COMPONENT DEFINITION (ASE_ECD)                                                                                                       |     |

|   | <ul><li>6.1 COMPONENT "SUBSET TOE SECURITY TESTING (FPT_TST)"</li><li>6.2 DEFINITION OF FPT_TST.2</li></ul>                                   |     |

|   | 6.3 TSF SELF TEST (FPT_TST)                                                                                                                   |     |

| 7 |                                                                                                                                               |     |

|   | 7.1 TOE SECURITY FUNCTIONAL REQUIREMENTS                                                                                                      |     |

|   | 7.1.1 Extended Components FCS_RNG.1 and FAU_SAS.1                                                                                             |     |

|   | 7.1.2 Subset of TOE testing                                                                                                                   |     |

|   | <ul> <li>7.1.3 Memory access control</li> <li>7.1.4 Support of Cipher Schemes</li> </ul>                                                      |     |

|   | 7.1.5 Data Integrity                                                                                                                          |     |

|   | 7.2 TOE SECURITY ASSURANCE REQUIREMENTS                                                                                                       | .40 |

|   | 7.2.1 Refinements<br>7.3 SECURITY REQUIREMENTS RATIONALE                                                                                      |     |

|   | 7.3.1 Rationale for the Security Functional Requirements                                                                                      |     |

|   | 7.3.2 Rationale of the Assurance Requirements                                                                                                 |     |

| 8 | TOE SUMMARY SPECIFICATION (ASE_TSS)                                                                                                           | .47 |

|   | 8.1 SF1: OPERATING STATE CHECKING                                                                                                             |     |

|   | <ul> <li>8.2 SF2: PHASE MANAGEMENT WITH TEST MODE LOCK-OUT</li> <li>8.3 SF3: PROTECTION AGAINST SNOOPING</li> </ul>                           |     |

| Γ | V0.3 Date: 2011-05-30 Page: 3/5                                                                                                               |     |

| 10  | APPENDIX                                                                       | 57 |

|-----|--------------------------------------------------------------------------------|----|

| 9.4 | GLOSSARY                                                                       | 55 |

| 9.3 |                                                                                |    |

| 9.2 |                                                                                |    |

| 9.1 | USER GUIDANCE                                                                  |    |

| 9 R | REFERENCES                                                                     | 53 |

| 8.8 | ASSIGNMENT OF SECURITY FUNCTIONAL REQUIREMENTS TO TOE'S SECURITY FUNCTIONALITY | 51 |

| 8.7 | SF7: NVM TEARING SAFE WRITE                                                    |    |

| 8.6 |                                                                                |    |

| 8.5 | SF5: VIRTUAL MEMORY SYSTEM (VMS)                                               | 49 |

| 8.4 | SF4: TSF SELF TEST                                                             |    |

|  | V0.3 | Date: | 2011-05-30 | Page: | 4/59 |

|--|------|-------|------------|-------|------|

|--|------|-------|------------|-------|------|

### List of figures:

| Figure 2-1: Block diagram of the SLE88CNFX6600PM hardware components            | 11 |

|---------------------------------------------------------------------------------|----|

| Figure 2-2: Block diagram of the SLE88CNFX6600PM Platform Support Layer (PSL)   | 12 |

| List of tables                                                                  |    |

| Table 1: Identification                                                         | 6  |

| Table 2: Production site in chip identification                                 | 16 |

| Table 3: Availability of functionality of the derivates:                        | 16 |

| Table 4: Augmentations of the assurance level of the TOE                        | 18 |

| Table 5: Threats according PP [1]                                               | 21 |

| Table 6: Additional threats due to TOE specific functions and augmentations     | 22 |

| Table 7: Organizational Security Policies according PP [1]                      | 23 |

| Table 8: Assumption according PP [1]                                            | 24 |

| Table 9: Objectives for the TOE according to PP [1]                             | 26 |

| Table 10: Additional objectives due to TOE specific functions and augmentations | 27 |

| Table 11: Security objectives for the environment according to PP [1]           | 27 |

| Table 12: Security Objective Rational                                           | 28 |

| Table 13: Security functional requirements defined in PP [1]                    |    |

| Table 14: Augmented security functional requirements                            |    |

| Table 15: Effective access rights (EAR) for data read/write operations          | 35 |

| Table 16: Assurance components                                                  | 40 |

| Table 17: Rational for additional SFR in the ST                                 | 41 |

| Table 18: Dependency for cryptographic operation requirement                    | 44 |

| Table 19: Mapping of SFR and SF                                                 | 52 |

| Table 20: User guidance                                                         | 53 |

| Table 21: Rules and standards                                                   | 53 |

| Table 22: Reference hash values of the PSL V3.22.11                             | 57 |

## **1** Security Target Introduction (ASE\_INT)

#### 1.1 Security Target and Target of Evaluation Reference

The title of this document is Security Target (ST) and comprises the Infineon Technologies Smart Card IC (Security Controller) SLE88CNFX6600PM, is internally registered under the development code m8864a13 and has the version number a13 with specific IC dedicated software.

The target of evaluation (TOE) SLE88CNFX6600PM / m8864a13 is described in the following. The Security Target has the revision 0.3 and is dated 2011-05-30.

The Target of Evaluation (TOE) is a smart card IC (Security Controller) as listed in Table 1 and its blocked derivatives listed in Table 3. The design step is a13.

The Security Target is based on the Protection Profile "Smartcard IC Platform Protection Profile" [1].

The Protection Profile and the Security Target are built in compliance with Common Criteria v3.1.

The ST takes into account all relevant current final interpretations.

|                                                                                                                                                                                                                                                                                                                  | Version    | Date       | Registration                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Target                                                                                                                                                                                                                                                                                                  | 0.3        | 2011-05-30 | M8864 A13                                                                                                                                                                                                                                                                                 |

| Security Target<br>Target of Evaluation<br>SLE88CNFX6600PM<br>SLE88CNFX6602PM<br>SLE88CNF6600PM<br>SLE88CNF6602PM<br>SLE88CNF5400PM<br>SLE88CNFX6600P<br>SLE88CNFX6602P<br>SLE88CNFX6600P<br>SLE88CNF6600P<br>SLE88CNF5400P<br>SLE88CNF5400P<br>SLE88CNF5400P<br>SLE88CNF5400P<br>SLE88CFX6600P<br>SLE88CFX6600P | 0.3<br>a13 | 2011-05-30 | M8864 A13<br>m8864XXX a13<br>m8867XXX a13<br>m8960XXX a13<br>m8954XXX a13<br>m8957XXX a13<br>m8957XXX a13<br>m8865XXX a13<br>m8868XXX a13<br>m8868XXX a13<br>m8855XXX a13<br>m8951XXX a13<br>m8958XXX a13<br>m8958XXX a13<br>m8971XXX a13<br>m8866XXX a13<br>m8866XXX a13<br>m8866XXX a13 |

| SLE88CFX6002P<br>SLE88CFX5400P<br>SLE88CF6600P<br>SLE88CF6602P<br>SLE88CF5400P                                                                                                                                                                                                                                   |            |            | m8962XXX a13<br>m8956XXX a13<br>m8956XXX a13<br>m8972XXX a13<br>all derivates with<br>PSL V3.22.11 and<br>guidance documentation                                                                                                                                                          |

Table 1: Identification

| Guidance<br>Documentation | Edition<br>2011-05               | 2011-05-31                 | SLE88 Family - SLE88CNFXxxxPM<br>PSL & Security Reference Manual                                                                                                                                                                                             |

|---------------------------|----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Edition<br>2009-12-19<br>Edition | 2009-12-19<br>July 02,2010 | SLE 88CNFX Family – Hardware Reference<br>User's Manual<br>SLE88CNFX Family Errata Sheet                                                                                                                                                                     |

| Protection Profile        | 2010-07-02<br>1.0                | 2007-06-15                 | Security IC Platform Protection Profile<br>PP0035                                                                                                                                                                                                            |

| Common Criteria           | Version 3.1<br>Revision 3        | 2009-July                  | Common Criteria for Information<br>Technology Security Evaluation<br>Part 1: Introduction and general model<br>CCMB-2009-07-001<br>Part 2: Security functional requirements<br>CCMB-2009-07-002<br>Part 3: Security Assurance Components<br>CCMB-2009-07-003 |

#### Remarks to the Target of Evaluation (TOE):

The TOE of this Security Target encloses the SLE88CNFX6600PM and seventeen different chip derivates. The hardware and the firmware of the SLE88CNFX6600PM and the seventeen derivates are identical (the version number is for all the a13 and the firmware version is for all the PSL V3.22.11, 660 kByte NVM, 256 kByte ROM and 32 kByte RAM). The differences between the derivates are the blocked crypto co-processor, the blocked contactless interfaces and the User NVM and User ROM size as shown in the following:

| SLE88CNFX6600PM:    | 628 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

|---------------------|------------------------------------------------------------------|

| SLE88CNFX6602PM:    | 628 kByte User NVM, 24 kByte User RAM, 160 kByte User ROM        |

| SLEOOCINFA0002FIVI. | 020 KDyle Usel INVIVI, 24 KDyle Usel RAIVI, 100 KDyle Usel ROIVI |

| SLE88CNFX5400PM:    | 508 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNF6600PM:     | 628 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNF6602PM:     | 628 kByte User NVM, 24 kByte User RAM, 160 kByte User ROM        |

| SLE88CNF5400PM:     | 508 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNFX6600P:     | 640 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNFX6602P:     | 640 kByte User NVM, 24 kByte User RAM, 160 kByte User ROM        |

| SLE88CNFX5400P:     | 520 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNF6600P:      | 640 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CNF6602P:      | 640 kByte User NVM, 24 kByte User RAM, 160 kByte User ROM        |

| SLE88CNF5400P:      | 520 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CFX6600P:      | 640 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CFX6602P:      | 640 kByte User NVM, 24 kByte User RAM, 184 kByte User ROM        |

| SLE88CFX5400P:      | 520 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CF6600P:       | 640 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

| SLE88CF6602P:       | 640 kByte User NVM, 24 kByte User RAM, 184 kByte User ROM        |

| SLE88CF5400P:       | 520 kByte User NVM, 24 kByte User RAM, 0 kByte User ROM          |

|                     |                                                                  |

neon

The TOE, called SLE88CNFX6600PM in the following description, stands for the SLE88CNFX6602PM, SLE88CNFX5400PM, SLE88CNF6600PM, SLE88CNF5400PM, SLE88CNFX6600P, SLE88CNFX6602P, SLE88CNFX6600P, SLE88CNF6600P, SLE88CNF5400P, SLE88CFX6600P, SLE88CFX600P, SLE88CFX60P, SLE8CFX60P, SL

The extension "M" in the product name denotes the Mifare<sup>™ 1</sup> compatible Interface and the "N" denotes the near filed communication standard (NFC) interface. If the product name is neither including extension "M" nor "N", it has the ISO7816 interfaces active only.

The derivates SLE88CFX6600P, SLE88CFX6602P, SLE88CFX5400P, SLE88CF6600P, SLE88CF6602P and SLE88CF5400P are the same hardware as the SLE88CNFX6600PM with the exception that the contactless communication via a near field communication standard (NFC) and the Mifare<sup>™</sup> compatible Interface classic protocol is blocked during the production process. The blocking is done by deactivating during the production test without physically changing the TOE

The derivates SLE88CNF6600PM, SLE88CNF6602PM, SLE88CNF5400PM, SLE88CNF6600P, SLE88CNF6602P, SLE88CNF5400P, SLE88CF6600P, SLE88CF6602P and SLE88CF5400P are not providing the functionality of the Crypto@1408Bit coprocessor. Therefore the functionality of the Advanced Crypto Engine Driver and the patch loader mode of the Loader Filter Driver are not provided by these derivates as described in the [SoftwareManual]. The functionality RSA cryptography and the functionality patch loader mode (Loader Filter Driver) of the security enforcing function SF2 are not provided by these derivates. Not including this functionality has no impact of any other security policy of the TOE.

The blocking of the EEPROM is done by setting the according value in the chip configuration page, which is not available to the user. The same means of blocking are also used for switching on and off the accessibility of the cryptographic co-processor Crypto@1408Bit, the NFC and/or the Mifare<sup>™</sup> compatible Interface protocol and also for the configuration of the ROM-sizes.

The memory settings are done during the production process by programming the physical startand end-address of the user available memory areas. The entire configuration page including also the other blocking information can not be changed by the user afterwards and is protected against manipulation.

The firmware version PSL V3.22.11 can be tailored by the user to remove functionality, which the user decides not to use. The functionality of each tailored version is described in the guidance documentation of the TOE. The process to tailor a PSL version is described in the guidance documentation.

The TOE can be delivered to the user with PSL already tailored according to the user choice for the derivate SLE88CNFX6602PM, SLE88CNF6602PM, SLE88CNFX6602P, SLE88CFX6602P and SLE88CF6602P.

For the derivates SLE88CNFX6600PM, SLE88CNFX5400PM, SLE88CNF6600PM, SLE88CNF5400PM, SLE88CNFX6600P, SLE88CNFX6600P, SLE88CNF5400P, SLE88CFX6600P, SLE88CFX6600P, SLE88CFX5400P, SLE88CF6600P and SLE88CF5400P, the TOE can be tailored by the user itself during his manufacturing process, as described in the guidance documentation.

A tailored PSL delivered on the TOE to the user does not include a code implementing functionality, which the user decided not to use. This, for example could be the SHA functionality, which is a part of SF6 according to P.Add-Functions. Not including the code implementing the SHA has no impact of any other security policy of the TOE, it is exactly equivalent to the situation where the user decides just not to use the SHA functionality.

A tailored PSL of the TOE could also for example exclude or deactivate the code implementing some security non enforcing functionality. Therefore this has no impact of any other security policy of the TOE.

| V0.3 | Date: | 2011-05-30 | Page: | 8/59 | ĺ |

|------|-------|------------|-------|------|---|

|------|-------|------------|-------|------|---|

<sup>&</sup>lt;sup>1</sup> Mifare<sup>TM</sup> is a trademark of NXP B.V.

The PSL can be delivered completely stored on the TOE or a part of the PSL can be delivered in form of precompiled binary files (.obj). The filenames and the corresponding hash values are listed in section 11 Appendix.

#### **1.2 Target of Evaluation overview**

The TOE comprises the Infineon Technologies Smart Card IC (Security Controller) SLE88CNFX6600PM with specific IC dedicated software.

This Security Target (ST) describes the TOE known as the Infineon Technologies AG security controller group as listed in Table 1 and gives a summary product description.

The TOE is a member of the Security Controller family SLE88 and meets the highest requirements in terms of performance and security.

The TOE is intended to be used in smart cards for particularly high security-relevant applications. The TOE provides a real 32-bit CPU-architecture. The major components of the core system are the CPU (Central Processing Unit), the MMU (Memory Management Unit) and MED (Memory Encryption/Decryption Unit). The TOE implements a full linear addressable memory space for each privilege level, a simple scalable Memory Management concept.

The PSL software is providing additionally functionality via an API to the Smartcard Embedded Software. The STS firmware is used for test purposes during start-up and the Flash Loader allows downloading user software to the NVM during the manufacturing process or in the field.

The two cryptographic co-processors serve the need of modern cryptography: The DES module provides Triple-DES with dual-key or triple-key hardware acceleration. The Asymmetric Crypto Co-processor, called Crypto@1408Bit in the following, provides basic functions for RSA and Elliptic Curve (EC) cryptography.

In this security target the TOE is described and a summary specification is given. The security environment of the TOE during its different phases of the lifecycle is defined. The assets are identified which have to be protected through the security policy. The threats against these assets are described. The security objectives and the security policy are defined, as well as the security requirements. These security requirements are built up of the security functional requirements as part of the security policy and the security assurance requirements. These are the steps during the evaluation and certification showing that the TOE meets the targeted requirements. In addition, the functionality of the TOE matching the requirements is described.

The assets, threats, security objectives and the security functional requirements are defined in this Security Target and in [1] and are referenced here. These requirements build up a minimal standard common for all Smartcards.

The security functions are defined here in the security target as property of this specific TOE. Here it is shown how this specific TOE fulfils the requirements for the standard defined in the Protection Profile [1].

| V0.3 | Date: | 2011-05-30 | Page: | 9/59 |  |

|------|-------|------------|-------|------|--|

|      |       |            |       |      |  |

### 2 Target of Evaluation Description

The TOE description helps to understand the specific security environment and the security policy. In this context the assets, threats, security objectives and security functional requirements can be employed. The following is a more detailed description of the TOE than in [1] as it belongs to the specific TOE.

#### 2.1 TOE Definition

The Target of Evaluation (TOE), the SLE88CNFX6600PM chip, is a smart card IC (Security Controller) meeting the highest requirements in terms of performance and security. It is manufactured by in a 0,13  $\mu$ m CMOS technology. The IC is intended to be used in smart cards for particularly security-relevant applications. That is based on its previous use as developing platform for smart card operating systems according to the lifecycle model (in [1]).

The term "User Software" is used in the following for all operating systems and applications stored and executed on the TOE. The TOE is the platform for the user software. The user software itself is not part of the TOE.

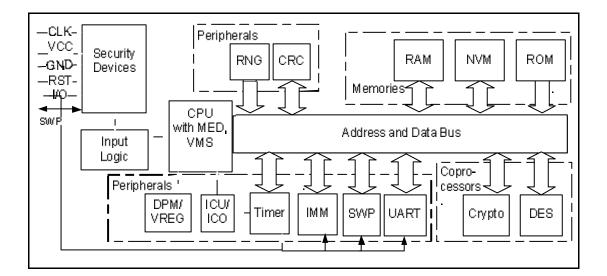

The SLE88CNFX6600PM, whose block diagram is shown in Figure 2-1, consists of a dedicated microprocessor (CPU) with a virtual memory system (VMS), several different memories, security logic, a timer and an interrupt-controlled I/O interface, an interface management module, a Single Wire Protocol slave module (SWP) and two co-processors. The RNG module integrated on the chip consists of a TRNG (True Random Number Generator).

The 32bit CPU is especially designed for smart card applications and provides powerful instructions for smart card applications. The memory comprises 32 KB of RAM, 184 KB of ROM and 660 KB of NVM. For the user 24 KB of RAM, 160 KB of ROM and 508 KB of NVM are minimal available depending on the derivate. It thus meets the requirements of the new generation of smartcard operating systems. The CPU accesses the memory via the integrated Memory Encryption and Decryption unit (MED). The access rights of the application to the memories can be controlled with the Virtual Memory System (VMS). Security, sleep mode and interrupt logic as well as the RNG are specially designed for smart card applications. The Sleep Mode logic (clock stop mode per ISO/IEC 7816-3) and the Supply-Shutdown Mode are used to reduce the overall power consumption. The timer permits easy implementation of communication protocols such as T=1 and all other time-critical operations. The input logic with uart-controlled I/O interface allows the smart card and terminal to be operated in parallel. The ICO unit of the input logic allows to operate the SLE88CNFX6600PM with a multiplication factor over the external clock signal or free running with maximum frequency. The Single Wire Protocol slave peripheral (SWP according to ETSI TS 102 613) connects an SWP master of the outside world via the SWP pad with the CPU of the TOE and contains a coprocessor for Mifare<sup>™</sup> compatible Interface data stream de- and encryption. The TRNG provides random number data meeting high demands for e.g. cryptographic algorithms (keys) and protocols (challenges, blinding values, padding etc.).

Four modules for cryptographic operations are implemented on the TOE. The coprocessor Crypto@1408BIT is used for calculation of asymmetric algorithms like RSA or Elliptic Curve (EC) cryptography. This module is especially designed for chipcard applications with respect to the security and power consumption. The DES module computes the complete DES algorithm within a few clock cycles. That module is especially designed to counter attacks like DPA or EMA. The CRC module generates a 16-bit checksum conforming to ISO/IEC 3309 or CCITT V.41 to provide for the integrity of received or transmitted data and also calculates the parity bits on a byte granularity. Additionally the module SHA (Secure Hash Algorithm) is included as software module.

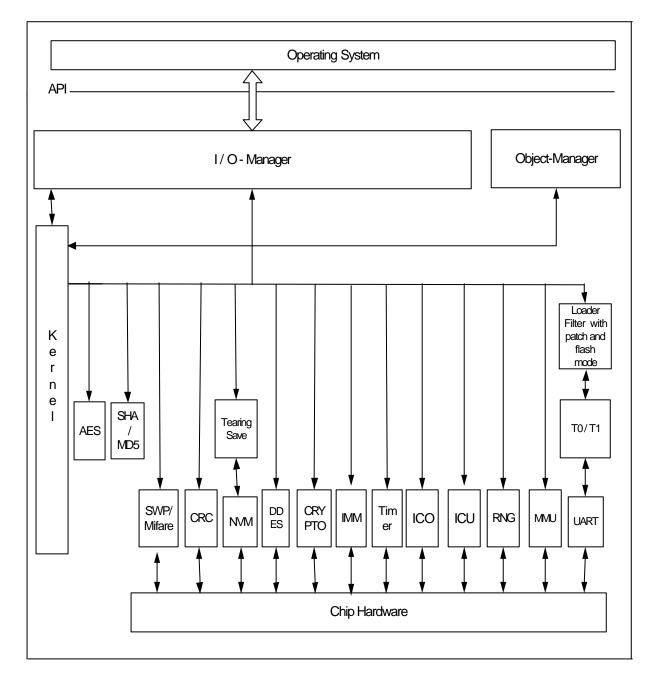

The firmware consists of two parts. The one is called platform support layer (PSL). It provides a convenient high level interface to the hardware devices like timers, UART (Universal Asynchronos Receiver Transmitter), Crypto@1408Bit, TRNG (Random Number Generator), NVM (Non Volatile

Memory), DES (Data Encryption Standard) and to the cryptographic functions AES (Advanced Encryption Standard), MD5, CRC (Cyclic Redundancy Check) and SHA (Secure Hash Algorithm).

The AES Encryption/Decryption Driver, the MD5 Generator Driver and the CRC Generator Driver are not in the scope of the certification and not part of the security features of the TOE.

The PSL provides the user (operating system) with the functionality to load code and data into the memory areas of the TOE in a secured process. The PSL hides all implementation specific details of a control operation performed at register level with a high security level of the implementation. The PSL is stored in ROM and NVM of the TOE. The use of the PSL is strongly recommended by the user guidance [SoftwareManual].

The other firmware part is the Self Test Software (STS), which controls the start-up of the chip. The STS configures all necessary parameters like keys for the MED. During the production test at the manufacturer the STS provides an interface to the test capabilities of the SLE88CNFX6600PM. The lock out of the test capabilities is also performed by the STS.

The TOE offers a new, improved standard of integrated security features, thereby meeting the requirements of all smart card applications such as information integrity, access control, mobile telephone, as well as uses in electronic funds transfer and healthcare systems.

To sum up, the TOE is a powerful smart card IC with a large amount of memory and special peripheral devices with both improved performance and optimized power consumption at minimal chip size. It therefore constitutes the basis for future smart card applications.

Figure 2-1: Block diagram of the SLE88CNFX6600PM hardware components

|  | V0.3 | Date: 2011-05-30 | Page: 11/59 |

|--|------|------------------|-------------|

|--|------|------------------|-------------|

Figure 2-2: Block diagram of the SLE88CNFX6600PM Platform Support Layer (PSL)

#### 2.2 Scope of the TOE

The TOE comprises the *hardware* of the smart card security controller, type SLE88CNFX6600PM, manufactured by Infineon, the associated *firmware* required for operation and provided in ROM and the associated software provided in ROM and NVM. The documents described in section 2.2.4 and listed in section 9.1 are supplied as a manual. In the following description, the term "manufacturer" is short term for the manufacturer of the TOE. The Smartcard Embedded Software respectively user software is not part of the TOE.

| V0.3 | Date: | 2011-05-30 | Page: | 12/59 |

|------|-------|------------|-------|-------|

#### 2.2.1 Hardware of the TOE

The hardware part of the TOE (cf. Figure 2-1) as defined in [1] is comprised of:

- Security devices comprising different sensors, filters, the selftest and the active shielding

- 32bit CPU with the subcomponents Memory Encryption and Decryption unit (MED3000) and Virtual Memory System (VMS) includes countermeasures against side-channel attacks.

- Peripheral modules comprising:

- Random Number Generator (RNG) including a true random number generator (TRNG) and a pseudo random number generator (PRNG)

The PRNG is not in the scope of the certification and not part of the security features of the TOE

- Interrupt module (ICU)

- Timer (TIM)

- Internal oscillator (ICO)

- Voltage regulator (VREG)

- Universal Asynchronous Receiver Transmitter (UART)

- Dynamic Power management

- Single Wire Protocol (SWP) slave peripheral including Mifare™ compatible Interface coprocessor

- Interface Management Module (IMM)

- CRC Module

- External memory comprising:

- 32 KB extended RAM

- 184 KB ROM, including the test routines (STS) and the PSL

- 660 KB nonvolatile memory NVM.

- Cryptographic devices comprising:

- Crypto@1408Bit for long integer modulo calculations, which are used in asymmetric algorithms like RSA

- DES accelerator (DES), used for fast calculations of the DES algorithm includes countermeasures against side-channel attacks

- Address and data bus (BUS)

Note 1:

The derivates SLE88CNF6600PM, SLE88CNF6602PM, SLE88CNF5400PM, SLE88CNF6600P, SLE88CNF6602P, SLE88CNF5400P, SLE88CF6600P, SLE88CF6602P and SLE88CF5400P are not providing the functionality of the Crypto@1408Bit cryptographic device. End of note.

|  |  | V0.3 | Date: | 2011-05-30 | Page: | 13/59 |  |

|--|--|------|-------|------------|-------|-------|--|

|--|--|------|-------|------------|-------|-------|--|

#### 2.2.2 Firmware and software of the TOE

The entire software/firmware of the IC consists of two different parts. The one is the PSL as high level interface to the hardware functions (**P**latform **S**upport Layer, IC Dedicated Support Software in [1]). The other part comprises the **S**elf **T**est **S**oftware (STS, IC Dedicated Support Software in [1]). The STS consists of test and initialization routines and the Mifare<sup>TM</sup> compatible Interface data de-/encryption. The STS routines are not accessible for the user software due to VMS access rights.

The software part (PSL) of the TOE (cf. Figure 2-2) as defined in [1] is comprised of:

- IO-Manager

- Kernel

- Object-Manager

- MD5 Generator Driver The MD5 Generator Driver is not in the scope of the certification and not part of the security features of the TOE

- CRC Generator Driver (CRC)

- Secure Hash Algorithm Driver (SHA)

- AES Encryption/Decryption Driver (AES) includes countermeasures against side-channel attacks. The AES Encryption/Decryption Driver is not in the scope of the certification and not part of the security features of the TOE

- NVM Driver (NVM)

- Tearing Save

- DDES Accelerator Driver (DDES)

- CRYPTO (Crypto@1408Bit) includes countermeasures against side-channel attacks

- Timer Device Driver

- Memory Management Driver (MMU)

- Internal Clock Oscillator Driver (ICO)

- Interrupt Subsystem Driver (ICU)

- Random Number Generator Driver (RNG)

- UART

- T=0/T=1 Protocol Driver (T0/T1)

- Loader Filter Driver with patch loader and flash loader mode

- IMM Driver

- SWP Driver

- Mifare<sup>™</sup> compatible Interface Driver

Note 2:

The derivates SLE88CNF6601PM, SLE88CNF6603PM, SLE88CNF5401PM, SLE88CNF6601P, SLE88CNF6603P, SLE88CNF5401P, SLE88CF6601P and SLE88CF6603P are not providing the functionality of the Crypto@1408Bit cryptographic device and the patch loader mode of the Loader

| V0.3 | Date: 2011-05-30 | Page: 14/59 |

|------|------------------|-------------|

neon

Filter Driver. End of note.

The above demarcations of the TOE result in the interfaces described below.

#### 2.2.3 Interfaces of the TOE

- The physical interface of the TOE to the external environment is the entire surface of the IC.

- The electrical interface of the TOE to the external environment is constituted by the pads of the chip, particularly the contacted RST, I/O0, CLK, SWP lines and supply lines VCC and GND.

- The data-oriented I/O interface to the TOE is formed by the I/O and SWP pads.

- The interface of the TOE to the operating system is constituted on the one hand by the PSL routine calls and on the other by the instruction set of the TOE.

- The interface of the TOE to the test routines is formed by the STS test routine call, i.e. entry to test mode (STS-TM entry).

- The derivates without extension "M" and "N" communicate with the contact-based interface according to ISO 7816/ETSI/EMV.

- The derivates with the extended "M" are used for the Mifare<sup>™</sup> compatible Interface contactless interface protocol and related memory management (classic 1k emulation), but can communicate also contact based via ISO 7816.

- The derivates with the extended "N" are used for the Single-Wire-Protocol (SWP) protocol according [ETSI TS 102 613], but can communicate also contact based via ISO 7816.

#### 2.2.4 Guidance documentation

The guidance documentation consists of the [HardwareManual], [SoftwareManual] and [ErrataSheet], which are containing the description of all interfaces of the software to the hardware relevant for programming the SLE88CNFX6600PM and the guidance to generate tailored PSL if necessary.

Finally the certification report will contain an overview of the recommendations to the software developer regarding the secure use of the platform SLE88CNFX6600PM. These recommendations are also included in the ordinary documentation.

The list of guidance documentation is given in section 9.1.

#### 2.2.5 Forms of delivery

Several delivery processes exist during the lifecycle of the SLE88CNFX6600PM. The documentation and software development tools including the PSL are delivered from phase 2/3 to phase 1 in form of data carriers and paper documentation.

The SLE88CNFX6600PM can be delivered in form of complete modules, in form of plain wafers or in an IC case (e.g. DSO20). Additionally the SLE88CNFX6600PM (TOE) can be delivered finished or with an unfinished PSL software. In this case the delivery components are including an additionally part of the PSL software. The user has to implement this part of the PSL software during the personalization process of the operating system as described in the guidance documentation to finish the TOE. The delivery can therefore be at the end of phase 3 or at the end of phase 4 according to [1]. Nevertheless in all four cases the extended test features of the TOE are removed. In this document are always all four cases mentioned to avoid incorrectness but from the security policy point of view all four cases are identical.

V0.3 Date: 2011-05-30 Page: 15/59

#### 2.2.6 Production sites

The TOE is produced in the production site Dresden. To distinguish different production sites the Chip Ident Mode data is coded as shown in Table 2.

The delivery measures are described in the ALC\_DVS aspect.

| Production Site | Chip Identification        |

|-----------------|----------------------------|

|                 | (first nibble, hex format) |

| Dresden         | 2                          |

#### 2.2.7 Availability of functionality

| TOE derivate    | Crypto@<br>1408Bit | ACE<br>driver    | Patch<br>Loader  | NFC              | Mifare™<br>compatible<br>Interface | SF1 to<br>SF7 |

|-----------------|--------------------|------------------|------------------|------------------|------------------------------------|---------------|

| SLE88CNFX6600PM | activated          | available        | available        | available        | available                          | available     |

| SLE88CNFX6602PM | activated          | available        | available        | available        | available                          | available     |

| SLE88CNFX5400PM | activated          | available        | available        | available        | available                          | available     |

| SLE88CNF6600PM  | deactivated        | not<br>available | not<br>available | available        | available                          | Note 3        |

| SLE88CNF6602PM  | deactivated        | not<br>available | not<br>available | available        | available                          | Note 3        |

| SLE88CNF5400PM  | deactivated        | not<br>available | not<br>available | available        | available                          | Note 3        |

| SLE88CNFX6600P  | activated          | available        | available        | available        | not<br>available                   | available     |

| SLE88CNFX6602P  | activated          | available        | available        | available        | not<br>available                   | available     |

| SLE88CNFX5400P  | activated          | available        | available        | available        | not<br>available                   | available     |

| SLE88CNF6600P   | deactivated        | not<br>available | not<br>available | available        | not<br>available                   | Note 3        |

| SLE88CNF6602P   | deactivated        | not<br>available | not<br>available | available        | not<br>available                   | Note 3        |

| SLE88CNF5400P   | deactivated        | not<br>available | not<br>available | available        | not<br>available                   | Note 3        |

| SLE88CFX6600P   | activated          | available        | available        | not<br>available | not<br>available                   | available     |

| SLE88CFX6602P   | activated          | available        | available        | not<br>available | not<br>available                   | available     |

|                 |                    |                  | V0.3             | Date: 201        | 1-05-30 Pa                         | age: 16/59    |

Table 3: Availability of functionality of the derivates:

| SLE88CFX5400P | activated   | available        | available        | not<br>available | not<br>available | available |

|---------------|-------------|------------------|------------------|------------------|------------------|-----------|

| SLE88CF6600P  | deactivated | not<br>available | not<br>available | not<br>available | not<br>available | Note 3    |

| SLE88CF6602P  | deactivated | not<br>available | not<br>available | not<br>available | not<br>available | Note 3    |

| SLE88CF5400P  | deactivated | not<br>available | not<br>available | not<br>available | not<br>available | Note 3    |

Note 3:

The SF1, SF3 to SF5 and the SF7 are completely available for these derivates. For the SF2 the patch loader mode of the Loader Filter Driver is not available. End of note.

The Crypto@1408Bit coprocessor is deactivated during the TOE life cycle phase 3. The production tests, which are done during the production (phase 3) as the TOE is in the test mode, are used to deactivate the Crypto@1408Bit coprocessor.

|  | V0.3 | Date: | 2011-05-30 | Page: | 17/59 |

|--|------|-------|------------|-------|-------|

|--|------|-------|------------|-------|-------|

## 3 Conformance Claims (ASE\_CCL)

#### 3.1 CC Conformance Claim

This Security Target (ST) and the TOE claim conformance to Common Criteria version v3.1 part 1 [2], part 2 [3] and part 3 [4].

Conformance of this ST is claimed for: Common Criteria part 2 extended and Common Criteria part 3 conformant.

Common Citteria part 2 extended and Common Citteria part 3 c

#### 3.2 PP Claim

This Security Target is in **strict conformance** to the Security IC Platform Protection Profile [1].

The Security IC Platform Protection Profile is registered and certified by the Bundesamt für Sicherheit in der Informationstechnik<sup>2</sup> (BSI) under the reference BSI-PP-0035, Version 1.0, dated 15.06.2007.

The security assurance requirements of the TOE are according to the Security IC Platform Protection Profile [1]. They are all drawn from Part 3 of the Common Criteria version v3.1.

The augmentations of the PP [1] are listed below.

Table 4: Augmentations of the assurance level of the TOE

| Assurance<br>Class       | Assurance<br>components | Description                                |

|--------------------------|-------------------------|--------------------------------------------|

| Life-cycle<br>support    | ALC_DVS.2               | Sufficiency of security measures           |

| Vulnerability assessment | AVA_VAN.5               | Advanced methodical vulnerability analysis |

#### 3.3 Package Claim

This Security Target does not claim conformance to a package of the PP [1].

The assurance level for the TOE is EAL5 augmented with the components ALC\_DVS.2 and AVA\_VAN.5.

#### 3.4 Conformance Rationale

This security target claims strict conformance only to one PP, the PP [1].

The Target of Evaluation (TOE) is a typical security IC as defined in PP chapter 1.2.2 comprising:

- the circuitry of the IC (hardware including the physical memories),

- configuration data, initialisation data related to the IC Dedicated Software and the behaviour of the security functionality

- the IC Dedicated Software with the parts

- the IC Dedicated Test Software,

<sup>&</sup>lt;sup>2</sup> Bundesamt für Sicherheit in der Informationstechnik (BSI) is the German Federal Authority for Information Security

| V0.3 Date: 2011-05-30 | Page: | 18/59 |

|-----------------------|-------|-------|

|-----------------------|-------|-------|

• the IC Dedicated Support Software.

The TOE is designed, produced and/or generated by the TOE Manufacturer.

Security Problem Definition:

nfineon

Following the PP [1], the security problem definition is enhanced by adding an additional threat, an additional organizational security policy and an additional assumption. Including these add-ons, the security problem definition of this security target is consistent with the statement of the security problem definition in the PP [1], as the security target claimed strict conformance to the PP [1].

Conformance Rationale:

The augmented organizational security policy P.Add-Functions, coming from the additional security functionality of the cryptographic algorithms, the augmented assumption A.Key-Function, related to the usage of key-depending function, and the threat memory access violation T.Mem-Access, due to specific TOE memory access control functionality, have been added. These add-ons have no impact on the conformance statements regarding CC [2] and PP [1], with following rational:

- The security target remains conformant to CC [2], claim 482 as the possibility to introduce additional restrictions is given.

- The security target fulfils the strict conformance claim of the PP [1] due to the application notes 5, 6 and 7 which apply here. By those notes the addition of further security functions and security services are covered, even without deriving particular security functionality from a threat but from a policy.

Due to additional security functionality, one coming from the cryptographic functions - O.Add-Functions, and due to the memory access control - O.Mem-Access, additional security objectives has been introduced. These add-ons have no impact on the conformance statements regarding CC [2] and PP [1], with following rational:

- The security target remains conformant to CC [2], claim 482 as the possibility to introduce additional restrictions is given.

- The security target fulfils the strict conformance of the PP [1] due to the application note 9 applying here. This note allows the definition of high-level security goals due to further functions or services provided to the Security IC Embedded Software.

Therefore, the security objectives of this security target are consistent with the statement of the security objectives in the PP [1], as the security target claimed strict conformance to the PP [1]. The security requirements of this security target are consistent with the statement of the security requirements in the PP [1], as the security target claimed strict conformance to the PP [1]. All security functional requirements defined in the PP [1] are included and completely defined in this ST. The security functional requirements listed in the following are all taken from Common Criteria part 2 [3] and additionally included and completely defined in this ST:

- FDP\_ACC.1 "Subset access control"

- FDP\_ACF.1 "Security attribute based access control"

- FMT\_MSA.1 "Management of security attributes"

- FMT\_MSA.3 "Static attribute initialisation"

- FMT\_SMF.1 "Specification of Management functions"

- FCS\_COP.1 "Cryptographic support"

- FDP\_SDI.2 "Stored data integrity monitoring and action"

The security functional requirement

• FPT\_TST.2 "Subset TOE security testing"(Requirement from [3])

are included and completely defined in this ST, section 6.

All assignments and selections of the security functional requirements are done in the PP [1] and in this security target in section 7.2.

The Assurance Requirements of the TOE obtain the Evaluation Assurance Level 5 augmented with the assurance components ALC\_DVS.2 and AVA\_VAN.5 for the TOE.

|  | V0.3 Date: 2011-05-30 | Page: 20/59 |

|--|-----------------------|-------------|

|--|-----------------------|-------------|

## 4 Security Problem Definition (ASE\_SPD)

The content of the PP [1] applies to this chapter completely.

#### 4.1 Threats

The threats are directed against the assets and/or the security functions of the TOE. For example, certain attacks are only one step towards a disclosure of assets while others may directly lead to a compromise of the application security. The more detailed description of specific attacks is given later on in the process of evaluation and certification. An overview on attacks is given in PP [1] section 3.2.

The threats to security are defined and described in PP [1] section 3.2.

| T.Phys-Manipulation | Physical Manipulation                   |

|---------------------|-----------------------------------------|

| T.Phys-Probing      | Physical Probing                        |

| T.Malfunction       | Malfunction due to Environmental Stress |

| T.Leak-Inherent     | Inherent Information Leakage            |

| T.Leak-Forced       | Forced Information Leakage              |

| T.Abuse-Func        | Abuse of Functionality                  |

| T.RND               | Deficiency of Random Numbers            |

Table 5: Threats according PP [1]

#### 4.1.1 Additional Threat due to TOE specific Functionality

The additional functionality of introducing sophisticated privilege levels and access control allows the secure separation between the operation system(s) and applications, the secure downloading of applications after personalization and enables multitasking by separating memory areas and performing access controls between different applications. Due to this additional functionality "area based memory access control" a new threat is introduced.

The Smartcard Embedded Software is responsible for its User Data according to the assumption "Treatment of User Data (A.Resp-Appl)". However, the Smartcard Embedded Software may comprise different parts, for instance an operating system and one or more applications. In this case, such parts may accidentally or deliberately access data (including code) of other parts, which may result in a security violation.

The TOE shall avert the threat "Memory Access Violation (T.Mem-Access)" as specified below.

T.Mem-Access Memory Access Violation

Parts of the Smartcard Embedded Software may cause security violations by accidentally or deliberately accessing restricted data (which may include code) or privilege levels. Any restrictions are defined by the security policy of the specific application context and must be implemented by the Smartcard Embedded Software.

Table 6: Additional threats due to TOE specific functions and augmentations

T.Mem-Access Memory Access Violation

For details see PP [1] section 3.2.

#### 4.1.2 Assets regarding the Threats

The primary assets concern the User Data which includes the user data as well as program code (Security IC Embedded Software) stored and in operation and the provided security services. These assets have to be protected while being executed and or processed and on the other hand, when the TOE is not in operation.

This leads to four primary assets with its related security concerns:

- SC1 Integrity of User Data and of the Security IC Embedded Software (while being executed/processed and while being stored in the TOE's memories),

- SC2 Confidentiality of User Data and of the Security IC Embedded Software (while being processed and while being stored in the TOE's memories)

- SC3 Correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- SC4 Continuous availability of random numbers

SC4 is an additional security service provided by this TOE which is the availability of random numbers. These random numbers are generated either by a true random number or a deterministic random number generator or by both, when a true random number is used as seed for the deterministic random number generator. Note that the generation of random numbers is a requirement of the PP [1].

To be able to protect the listed assets the TOE shall protect its security functionality as well. Therefore critical information about the TOE shall be protected. Critical information includes:

- logical design data, physical design data, IC Dedicated Software, and configuration data

- Initialisation Data and Pre-personalisation Data, specific development aids, test and characterisation related data, material for software development support, and reticles.

The information and material produced and/or processed by the TOE Manufacturer in the TOE development and production environment (Phases 2 up to TOE Delivery) can be grouped as follows:

- logical design data,

- physical design data,

- IC Dedicated Software, Security IC Embedded Software, Initialisation Data and Prepersonalisation Data,

- specific development aids,

- test and characterisation related data,

- material for software development support, and

- reticles and products in any form

as long as they are generated, stored, or processed by the TOE Manufacturer.

For details see PP [1] section 3.1.

#### 4.2 Organizational Security Policies

The TOE has to be protected during the first phases of their lifecycle (phases 2 up to TOE delivery which can be after phase 3 or phase 4). Later on each variant of the TOE has to protect itself. The organisational security policy covers this aspect.

P.Process-TOE Protection during TOE Development and Production

An accurate identification must be established for the TOE. This requires that each instantiation of the TOE carries this unique identification.

The organisational security policies are defined and described in PP [1] section 3.3. Due to the augmentations of PP [1] an additional policy is introduced and described in the next chapter.

Table 7: Organizational Security Policies according PP [1]

| P.Process-TOE | Protection during TOE Development and Production |

|---------------|--------------------------------------------------|

|---------------|--------------------------------------------------|

#### 4.2.1 Augmented Organizational Security Policy

Due to the augmentations of the PP [1] an additional policy is introduced.

The TOE provides specific security functionality, which can be used by the Smartcard Embedded Software. In the following specific security functionality is listed which is not derived from threats identified for the TOE's environment because it can only be decided in the context of the smartcard application, against which threats the Smartcard Embedded Software will use the specific security functionality.

The IC Developer / Manufacturer must apply the policy "Additional Specific Security Functionality (P.Add-Functions)" as specified below.

P.Add-Functions Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Smartcard Embedded Software:

- Data Encryption Standard (DES),

- Triple Data Encryption Standard (3DES)

- Secure Hash Algorithm (SHA)

#### 4.3 Assumptions

The TOE assumptions on the operational environment are defined and described in PP [1] section 3.4.

The assumptions concern the phases where the TOE has left the chip manufacturer.

A.Process-Sec-IC Protection during Packaging, Finishing and Personalization

It is assumed that security procedures are used after delivery of the TOE by the TOE Manufacturer up to delivery to the end-consumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

A.Plat-Appl Usage of Hardware Platform

The support of cipher schemas needs to make an additional assumption.

Table 8: Assumption according PP [1]

| A.Process-Sec-IC | Protection during Packaging, Finishing and Personalization |

|------------------|------------------------------------------------------------|

| A.Plat-Appl      | Usage of Hardware Platform                                 |

| A.Resp-Appl      | Treatment of User Data                                     |

|  | V0.3 | Date: 2011-05-30 | Page: 24/59 |

|--|------|------------------|-------------|

|--|------|------------------|-------------|

#### 4.3.1 Augmented Assumptions

The developer of the Smartcard Embedded Software must ensure the appropriate "Usage of Keydependent Functions (A.Key-Function)" while developing this software in Phase 1 as specified below.

A.Key-Function Usage of Key-dependent Functions

Key-dependent functions (if any) shall be implemented in the Smartcard Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

Note that here the routines which may compromise keys when being executed are part of the Smartcard Embedded Software. In contrast to this the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines which are part of the TOE

For details see PP [1] section 3.4.

|  | V0.3 | Date: | 2011-05-30 | Page: | 25/59 |

|--|------|-------|------------|-------|-------|

|--|------|-------|------------|-------|-------|

## 5 Security objectives (ASE\_OBJ)

nfineon

This section shows the subjects and objects where are relevant to the TOE. A short overview is given in the following.

The user has the following standard high-level security goals related to the assets:

- SG1 maintain the integrity of User Data and of the Security IC Embedded Software

- SG2 maintain the confidentiality of User Data and of the Security IC Embedded Software

- SG3 maintain the correct operation of the security services provided by the TOE for the Security IC Embedded Software

- SG4 provision of random numbers.

#### 5.1 Security objectives for the TOE

The security objectives of the TOE are defined and described in PP [1] section 4.1.

| O.Phys-Manipulation | Protection against Physical Manipulation        |

|---------------------|-------------------------------------------------|

| O.Phys-Probing      | Protection against Physical Probing             |

| O.Malfunction       | Protection against Malfunction                  |

| O.Leak-Inherent     | Protection against Inherent Information Leakage |

| O.Leak-Forced       | Protection against Forced Information Leakage   |

| O.Abuse-Func        | Protection against Abuse of Functionality       |

| O.Identification    | TOE Identification                              |

| O.RND               | Random Numbers                                  |

#### Table 9: Objectives for the TOE according to PP [1]

The TOE provides "Additional Specific Security Functionality (O.Add-Functions)" as specified below.

O.Add-Functions Additional Specific Security Functionality

The TOE must provide the following specific security functionality to the Smartcard Embedded Software:

- Data Encryption Standard (DES),

- Triple Data Encryption Standard (3DES),

- Secure Hash Algorithm (SHA).

The TOE shall provide "Area based Memory Access Control (O.Mem-Access)" as specified below.

O.Mem-Access Area based Memory Access Control

The TOE must provide the Smartcard Embedded Software with the capability to define restricted access memory areas. The TOE must then enforce the partitioning of such memory areas so that access of

| V0.3 | Date: | 2011-05-30 | Page: | 26/59 |

|------|-------|------------|-------|-------|

|      |       |            | -     | -     |

software to memory areas and privilege levels is controlled as required, for example, in a multi-application environment.

Table 10: Additional objectives due to TOE specific functions and augmentations

| O.Add-Functions | Additional specific security functionality |

|-----------------|--------------------------------------------|

| O.Mem-Access    | Area based Memory Access Control           |

#### 5.2 Security Objectives for the development and operational Environment

The security objectives for the security IC embedded software development environment and the operational environment is defined in PP [1] section 4.2 and 4.3. The table below lists the security objectives.

| Table 11. Security objectives for the environment according to PP [ | Security objectives for the environment according to PP [ | 'P [1] |

|---------------------------------------------------------------------|-----------------------------------------------------------|--------|

|---------------------------------------------------------------------|-----------------------------------------------------------|--------|

| Phase 1                         | OE.Plat-Appl      | Usage of Hardware Platform                        |

|---------------------------------|-------------------|---------------------------------------------------|

|                                 | OE.Resp-Appl      | Treatment of User Data                            |

| Phase 5 – 6<br>optional Phase 4 | OE.Process-Sec-IC | Protection during composite product manufacturing |

#### 5.2.1 Clarification of "Usage of Hardware Platform (OE.Plat-Appl)"

Regarding the cryptographic services this objective of the environment has to be clarified. The TOE supports cipher schemes as additional specific security functionality. If required the Smartcard Embedded Software shall use these cryptographic services of the TOE and their interface as specified. When key-dependent functions implemented in the Smartcard Embedded Software are just being executed, the Smartcard Embedded Software must provide protection against disclosure of confidential data (User Data) stored and/or processed in the TOE by using the methods described under "Inherent Information Leakage (T.Leak-Inherent)" and "Forced Information Leakage (T.Leak-Forced)".

The objectives of the environment regarding the memory, software and firmware protection and the SFR and peripheral-access-rights-handling have to be clarified. For the separation of different applications the Smartcard Embedded Software (Operating System) may implement a memory management scheme based upon security functions of the TOE.

#### 5.2.2 Clarification of "Treatment of User Data (OE.Resp-Appl)"

Regarding the cryptographic services this objective of the environment has to be clarified. By definition cipher or plain text data and cryptographic keys are User Data. The Smartcard Embedded Software shall treat these data appropriately, use only proper secret keys (chosen from a large key space) as input for the cryptographic function of the TOE and use keys and functions appropriately in order to ensure the strength of cryptographic operation.

This means that keys are treated as confidential as soon as they are generated. The keys must be unique with a very high probability, as well as cryptographically strong. For example, it must be ensured that it is beyond practicality to derive the private key from a public key if asymmetric algorithms are used. If keys are imported into the TOE and/or derived from other keys, quality and confidentiality must be maintained. This implies that appropriate key management has to be realised in the environment.

Regarding the memory, software and firmware protection and the SFR and peripheral access rights handling these objectives of the environment has to be clarified. The treatment of User Data is also required when a multi-application operating system is implemented as part of the Smartcard Embedded Software on the TOE. In this case the multi-application operating system should not

|  | V0.3 | Date: | 2011-05-30 | Page: | 27/59 |

|--|------|-------|------------|-------|-------|

|--|------|-------|------------|-------|-------|

disclose security relevant user data of one application to another application when it is processed or stored on the TOE.

## 5.2.3 Clarification of "Protection during Composite product manufacturing (OE.Process-Sec-IC)"

The protection during packaging, finishing and personalization includes also the personalization process (Flash Loader software) and the personalization data (TOE software components) during Phase 4, Phase 5 and Phase 6.

#### 5.3 Security Objectives Rationale

The security objectives rationale of the TOE are defined and described in PP [1] section 4.4. For organizational security policy P.Add-Functions, OE.Plat-Appl and OE.Resp-Appl the rationale is given in the following description.

| Assumption, Threat or<br>Organisational Security Policy | Security Objective           |

|---------------------------------------------------------|------------------------------|

| P.Add-Functions                                         | O.Add-Functions              |

| A.Key-Function                                          | OE.Plat-Appl<br>OE.Resp-Appl |

| T.Mem-Access                                            | O.Mem-Access                 |

The justification related to the security objective "Additional Specific Security Functionality (O.Add-Functions)" is as follows: Since O.Add-Functions requires the TOE to implement exactly the same specific security functionality as required by P.Add-Functions; the organisational security policy is covered by the objective.

Nevertheless the security objectives O.Leak-Inherent, O.Phys-Probing, O.Malfunction, O.Phys-Manipulation and O.Leak-Forced define how to implement the specific security functionality required by P.Add-Functions. (Note that these objectives support that the specific security functionality is provided in a secure way as expected from P.Add-Functions.) Especially O.Leak-Inherent and O.Leak-Forced refer to the protection of confidential data (User Data or TSF data) in general. User Data are also processed by the specific security functionality required by P.Add-Functions.

Compared to PP [1] clarification has been made for the security objective "Usage of Hardware Platform (OE.Plat-Appl)": If required the Smartcard Embedded Software shall use these cryptographic services of the TOE and their interface as specified. In addition, the Smartcard Embedded Software must implement functions which perform operations on keys (if any) in such a manner that they do not disclose information about confidential data. The non disclosure due to leakage A.Key-Function attacks is included in this objective OE.Plat-Appl. This addition ensures that the assumption A.Plat-Appl is still covered by the objective OE.Plat-Appl although additional functions are being supported according to O.Add-Functions.

Compared to the PP [1] a clarification has been made for the security objective "Treatment of User Data (OE.Resp-Appl)": By definition cipher or plain text data and cryptographic keys are User Data. So, the Smartcard Embedded Software will protect such data if required and use keys and functions appropriately in order to ensure the strength of cryptographic operation. Quality and confidentiality must be maintained for keys that are imported and/or derived from other keys. This implies that appropriate key management has to be realised in the environment. That is expressed by the assumption A.Key—Function which is covered from OE.Resp–Appl. These measures make sure that the assumption A.Resp-Appl is still covered by the security objective OE.Resp-Appl although additional functions are being supported according to P.Add-Functions.

| V0.3 | Date: | 2011-05-30 | Page: | 28/59 |

|------|-------|------------|-------|-------|

|------|-------|------------|-------|-------|

Compared to the PP [1] an enhancement regarding memory area protection has been established. The clear definition of privilege levels for operated software establishes the clear separation of different restricted memory areas for running the firmware, downloading and/or running the operating system and to establish a clear separation between different applications. Nevertheless, it is also possible to define a shared memory section where separated applications may exchange defined data. The privilege levels clearly define by using a hierarchical model the access right from one level to the other. These measures ensure that the threat T.Mem-Access is clearly covered by the security objective O.Mem-Access.

The justification of the additional policy and the additional assumption show that they do not contradict to the rationale already given in the Protection Profile for the assumptions, policy and threats defined there.

|  |  | ate: 2011-05-30 | Page: 29/59 |

|--|--|-----------------|-------------|

|--|--|-----------------|-------------|

### 6 Extended Component Definition (ASE\_ECD)

There are four extended components defined and described for the TOE:

- the family **FCS\_RNG** at the class FCS Cryptographic Support

- the family FMT\_LIM at the class FMT Security Management

- the family FAU\_SAS at the class FAU Security Audit

- the component **FPT\_TST.2** at the class FPT Protection of the TSF

The extended components FCS\_RNG, FMT\_LIM and FAU\_SAS are defined and described in PP [1] section 5. The component FPT\_TST.2 is defined in the following.

#### 6.1 Component "Subset TOE security testing (FPT\_TST)"

The security is strongly dependent on the correct operation of the security functions. Therefore, the TOE shall support that particular security functions or mechanisms are tested in the operational phase (Phase 7). The tests can be initiated by the Smartcard Embedded Software and/or by the TOE or is done automatically and continuously.

Part 2 of the Common Criteria provides the security functional component "TSF testing (FPT\_TST.1)". The component FPT\_TST.1 provides the ability to test the TSF's correct operation.

For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verification of the integrity of TSF data and of the stored TSF executable code which might violate the security policy. Therefore, the functional component "Subset TOE security testing (FPT\_TST.2)" of the family TSF self test has been newly created. This component allows that particular parts of the security mechanisms and functions provided by the TOE are tested.

#### 6.2 Definition of FPT\_TST.2

The functional component "Subset TOE security testing (FPT\_TST.2)" has been newly created (Common Criteria Part 2 extended). This component allows that particular parts of the security mechanisms and functions provided by the TOE can be tested after TOE Delivery or are tested automatically and continuously during normal operation transparent for the user. This security functional component is used instead of the functional component FPT\_TST.1 from Common Criteria Part 2. For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verifying the integrity of TSF data and stored TSF executable code which might violate the security policy.

The functional component "Subset TOE testing (FPT\_TST.2)" is specified as follows (Common Criteria Part 2 extended).

#### 6.3 TSF self test (FPT\_TST)

Family BehaviorThe Family Behavior is defined in [3] section 15.14 (442, 443).Component levelling

- FPT\_TST.1: The component FPT\_TST.1 is defined in [3] section 15.14 (444, 445, 446).

- FPT\_TST.2: Subset TOE security testing, provides the ability to test the correct operation of particular security functions or mechanisms. These tests may be performed at startup, periodically, at the request of the authorized user, or when other conditions are met. It also provides the ability to verify the integrity of TSF data and executable code.

Management: FPT\_TST.2

The following actions could be considered for the management functions in FMT:

- management of the conditions under which subset TSF self testing occurs, such as during initial start-up, regular interval or under specified conditions

- management of the time of the interval appropriate.

Audit: FPT\_TST.2

There are no auditable events foreseen.

| FPT_TST.2        | Subset TOE testing   |

|------------------|----------------------|

| Hierarchical to: | No other components. |

Dependencies: No dependencies

FPT\_TST.2.1: The TSF shall run a suite of self tests [selection: during initial start-up, periodically during normal operation, at the request of the authorized user, and/or at the conditions [assignment: conditions under which self test should occur]] to demonstrate the correct operation of [assignment: functions and/or mechanisms].

|--|

## 7 Security Requirements (ASE\_REQ)

For this section the PP [1] section 6 can be applied completely.

#### 7.1 TOE Security Functional Requirements

The security functional requirements (SFR) for the TOE are defined and described in the PP [1] section 6.1 and in the following description.

The Table 13 provides an overview of the functional security requirements of the TOE, defined in the PP [1] section 6.1. In the last column it is marked if the requirement is refined. The refinements are also valid for this ST.

|           | Security Functional Requirement              | Refined in PP [1] |

|-----------|----------------------------------------------|-------------------|

|           |                                              |                   |

| FRU_FLT.2 | "Limited fault tolerance"                    | Yes               |

| FPT_FLS.1 | "Failure with preservation of secure state"  | Yes               |

| FMT_LIM.1 | "Limited capabilities"                       | No                |

| FMT_LIM.2 | "Limited availability"                       | No                |