# **PUBLIC**

# Common Criteria Information Technology Security Evaluation

# **Project Crow V**

# **Security Target Lite of**

Samsung S3CT9P3

16-bit RISC Microcontroller

for Smart Card with

optional Secure RSA and ECC Library

including specific IC Dedicated Software

Version 1.2 23<sup>rd</sup> February 2018

# **REVISION HISTORY**

# **UPDATES:**

| Version | Date                            | Modification                          |

|---------|---------------------------------|---------------------------------------|

| 1.0     | 23 <sup>rd</sup> March 2012     | Creation                              |

| 1.1     | 27 <sup>th</sup> September 2017 | Update SAN version                    |

| 1.2     | 23 <sup>rd</sup> February 2018  | Update SAN version                    |

| 1.2     |                                 | The chapter 1.2.2,6.1,7.1 are updated |

|         |                                 |                                       |

|         |                                 |                                       |

|         |                                 |                                       |

|         |                                 |                                       |

|         |                                 |                                       |

Version 1.2 Page 2 of 64

# **CONTENTS**

| 1 | ST I                     | NTRODUCTION                                                          | 4            |

|---|--------------------------|----------------------------------------------------------------------|--------------|

|   | 1.1<br>1.2<br>1.3<br>1.4 | SECURITY TARGET AND TOE REFERENCE.  TOE OVERVIEW AND TOE DESCRIPTION | 4<br>11      |

| 2 | COI                      | NFORMANCE CLAIMS                                                     | . 12         |

|   | 2.1<br>2.2<br>2.3<br>2.4 | CC CONFORMANCE CLAIM                                                 | . 12<br>. 12 |

| 3 | SEC                      | CURITY PROBLEM DEFINITION                                            | . 14         |

|   | 3.1<br>3.2<br>3.3<br>3.4 | DESCRIPTION OF ASSETS                                                | . 15<br>. 20 |

| 4 | SEC                      | CURITY OBJECTIVES                                                    | . 23         |

|   | 4.1<br>4.2<br>4.3<br>4.4 | SECURITY OBJECTIVES FOR THE TOE                                      | . 26<br>. 27 |

| 5 | EXT                      | ENDED COMPONENTS DEFINITION                                          | . 31         |

|   | 5.1<br>5.2<br>5.3        | DEFINITION OF THE FAMILY FCS_RNG                                     | . 32         |

| 6 | IT S                     | ECURITY REQUIREMENTS                                                 | . 35         |

|   | 6.1<br>6.2<br>6.3        | SECURITY FUNCTIONAL REQUIREMENTS FOR THE TOE                         | . 46         |

| 7 | TOE                      | SUMMARY SPECIFICATION                                                | . 56         |

|   | 7.1                      | LIST OF SECURITY FUNCTIONAL REQUIREMENTS                             | . 56         |

| 8 | ANN                      | NEX                                                                  | . 61         |

|   | 8.1<br>8.2<br>8.3        | GLOSSARYABBREVIATIONS                                                | . 62         |

# 1 ST INTRODUCTION

- 2 This introductory chapter contains the following sections:

- 1.1 Security Target and TOE Reference

- 1.2 TOE Overview and TOE Description

- 1.3 Interfaces of the TOE

- 1.4 TOE Intended Usage

# 1.1 Security Target and TOE Reference

- The Security Target version is 1.2 and dated 23<sup>rd</sup> February 2018.

- 4 The Security Target is based on

- [5] Eurosmart, Security IC Platform Protection Profile, Version 1.0, June 2007, BSI-PP-0035.

- 5 The Protection Profile and the Security Target are built on *Common Criteria version 3.1*.

- Title: Security Target of **S3CT9P3** 16-Bit RISC Microcontroller for Smart Cards with optional Secure RSA and ECC Library including specific IC Dedicated Software

- Target of Evaluation: **S3CT9P3** 16-Bit RISC Microcontroller for Smart Cards, Revision 0 with optional Secure RSA and ECC Library (Version 2.0) including specific IC Dedicated Software

- Provided by: Samsung Electronics Co., Ltd.

- Common Criteria version:

- [1] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and general model, Version 3.1, Revision 3, July 2009, CCMB-2009-07-001.

- [2] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 2: Security Functional Components, Version 3.1, Revision 3, July 2009, CCMB-2009-07-002.

- [3] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 3: Security Assurance Components, Version 3.1, Revision 3, July 2009, CCMB-2009-07-003.

- [4] Common Criteria, Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1, Revision 3, July 2009, CCMB-2009-07-004.

# 1.2 TOE Overview and TOE Description

# 1.2.1 Introduction

The Target of Evaluation (TOE), the S3CT9P3 revision 0 microcontroller with optional Secure RSA/ECC Library version 2.0, featuring the TORNADO™2MX2 cryptographic coprocessor, is a smartcard integrated circuit which is composed of a processing unit, security components, contact based I/O ports, hardware circuit for testing purpose during the manufacturing process and volatile and non-volatile memories (hardware). The TOE also includes any IC Designer/Manufacturer proprietary IC Dedicated Software as long as it physically exists in the smartcard integrated circuit after being delivered by the IC Manufacturer. Such software (also known as IC firmware) is used for testing purpose during the manufacturing process but also provides additional services to facilitate the usage of the hardware and/or to provide additional services, including optional RSA/ECC asymmetric cryptography library and AIS31 compliant random number generator ([6]). The RSA/ECC library further includes the functionality of hash computation. The use for keyed hash operations like HMAC or similar security critical operations involving keys and other secrets, is not subject of this TOE and requires specific security improvements and DPA analysis including the operating system, which is not part of this TOE. However, this functionality is intended to be used for

ELECTRONICS Version 1.2 Page 4 of 64

- signature generation and verification only. All other software is called Smartcard Embedded Software and is not part of the TOE.

- Regarding the RSA and ECC library, the user has the possibility to tailor this IC Dedicated Software part of the TOE during the manufacturing process by deselecting the RSA and ECC library. Hence the TOE can be delivered with or without the functionality of the RSA and ECC library what's resulting in two TOE configurations. This is considered in this Security Target and corresponding notes (indicated by "optional") are added where required. If the user decides not to use the RSA/ECC crypto library, the library is not delivered to the user and the accompanying "Additional Specific Security Functionality (O.Add-Functions)" RSA and Elliptic Curve Cryptography (ECC) is not provided by the TOE. Deselecting RSA and ECC library means excluding the code implementing functionality, which the user decided not to use. Excluding the code of the deselected functionality has no impact on any other security policy of the TOE, it is exactly equivalent to the situation where the user decides just not to use the functionality.

8

# 1.2.2 TOE Definition

- 9 The **S3CT9P3** single-chip CMOS micro-controller is designed and packaged specifically for "Smart Card" applications.

- The CalmRISC16 CPU architecture of the **S3CT9P3** microcontroller follows the Harvard style, that is, it has separate program memory and data memory. Both instruction and data can be fetched simultaneously without causing a stall, using separate paths for memory access.

- 11 The main security features of the S3CT9P3 integrated circuit are:

- Security sensors or detectors including High and Low Temperature detectors, High and Low Frequency detectors, High and Low Supply Voltage detectors, Supply Voltage Glitch detectors, Light detector and the Passivation Removing Detector

- Active Shields against physical intrusive attacks

- Dedicated tamper-resistant design based on synthesizable glue logic and secure topology

- Dedicated hardware mechanisms against side-channel attacks such as Internal Variable Clock, Random Current Generator, Random Waits Generator, RAM and EEPROM encryption mechanisms

- Secure DES Symmetric Cryptography support

- Secure TORNADO™2MX2 coprocessor for RSA and ECC Asymmetric Cryptographic Support

- A Hardware True Random Number Generator (DTRNG) that meet P2 class of BSI-AIS31 (German Metric)

- The IC Dedicated Software includes:

- A modular arithmetic library for RSA and ECC (with SHA) Asymmetric Cryptography support (optional)

- A DTRNG library built around Hardware DTRNG together with a DTRNG application note that meets the P2 class of BSI-AIS31 (German Metric)

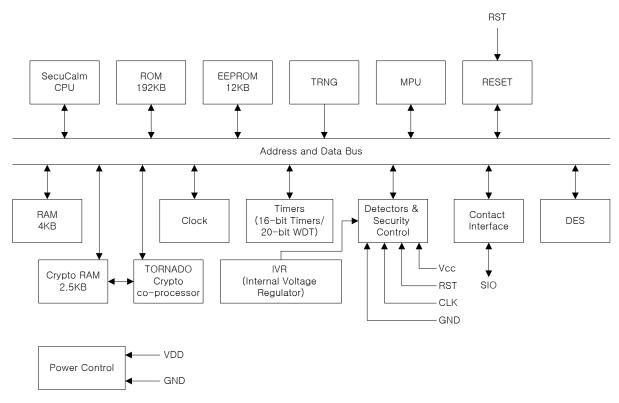

- 12 The main hardware blocks of the **S3CT9P3** Integrated Circuit are described in **Figure 1** below:

ECTRONICS Version 1.2 Page 5 of 64

Figure 1 S3CT9P3 Block Diagram

- \*Note that only the Triple DES algorithm belongs to the TOE, not the Single DES.

- 14 The TOE consists of the following Hardware and Software:

# **TOE Hardware**

- 12K bytes EEPROM/4K bytes RAM/2.5K bytes Crypto. RAM/192K bytes User ROM/8K bytes Test ROM

- 16-bit Central Processing Unit (CPU)

- Internal Voltage Regulator (IVR)

- Power Control

- Detectors & Security control(DSC)

- Random number generator

- Memory Protection Unit (MPU)

- Triple DES cryptographic coprocessor with 112 or 168 bits key size

- TORNADO™2MX2 supporting modular multiplications for the operand size up to 2080-bit and modular additions/subtractions for the operand size up to 512-bit

- Hardware UART for contact I/O modes (IO)

- Address & data buses (BUS)

- Clock control

- Reset Control

- Timers

Version 1.2 Page 6 of 64

## **TOE Software**

- 15 The TOE software comprises the following components:

- Test ROM code that is used for testing the chip during production

- The TORNADO™2MX2 Secure RSA/ECC library (optional)

TORNADO™ is a hardware coprocessor for high speed modular multiplications, modular additions and modular subtractions.

The TORNADO™2MX2 Secure RSA/ECC library is a software library built on the TORNADO™2MX2 coprocessor that provides high level interface for RSA and ECC cryptographic algorithms.

The RSA functions of the library included in the TOE are:

- RSA\_KeyGen\_Secure (RSA public/private key pair generation)

- TND\_RSA\_SigSTD\_Secure (RSA signature generation with the standard method)

- TND\_RSA\_SigCRT\_Secure (RSA signature generation with the CRT method)

- TND\_RSA\_Verify (RSA signature verification)

The functions TND\_RSA\_SigSTD\_Secure and TND\_RSA\_SigCRT\_Secure have some countermeasure against SPA, DPA and DFA attacks. Also, the RSA\_KeyGen\_Secure function implements some countermeasures against SPA and DFA attacks.

The TORNADO™2MX2 Secure RSA/ECC library provides a set of functions to implement elliptic curve cryptography algorithms. In particular it provides some functions to implement ECDSA signature and ECDH key exchange protocols. The library implements ECC for prime field and general curve for bit size from 192-bit to 512-bit and the only certain curves are in the scope of this evaluation. The ECC functions of the library included in the TOE are:

- ECDSA\_keygen (Generate ephemeral or static key pairs for ECDSA signature generation)

- ECDSA\_sign\_digest (ECDSA signature generation for a message digest)

- ECDSA\_verify\_digest (ECDSA signature verification for a message digest)

- ECDH\_generate (ECDH secret key derivation)

The functions ECDSA\_keygen and ECDSA\_sign\_digest have some countermeasure against SPA, DPA and DFA. The function ECDSA\_verify\_digest has some countermeasure against DFA. The function ECDH\_generate can be used with ephemeral or static private keys. It has some countermeasure against SPA, DPA and DFA for protecting the private key. The base point is assumed to be public.

Note1) The RSA/ECC library supports any valid elliptic curves over prime fields of size from 192-bit to 512-bit. However, standard curves listed below whose security has been proven are in the scope of this evaluation.

- 1) [NIST curves, 20]: Curves P-192, P-224, P-256, P-384

- 2) [Brainpool curves, 16]: brainpoolP192r1, brainpoolP192t1, brainpoolP224r1, brainpoolP224r1, brainpoolP256r1, brainpoolP256r1, brainpoolP320r1, brainpoolP320t1, brainpoolP384r1, brainpoolP384r1, brainpoolP512r1,

- 3) [SEC-recommended curves, 17]: secp192k1, secp192r1, secp224k1, secp224r1, secp256k1, secp256r1, secp384r11

The TORNADO™2MX2 Secure RSA/ECC library provides the following functions for calculating hash (digest) values using the SHA224, SHA256, SHA384 and SHA 512 algorithm as specified in [15], but, only functions related to SHA224, SHA256, SHA384 and SHA 512 are within the scope of this evaluation:

LECTRONICS Version 1.2 Page 7 of 64

- SHA224\_init, SHA224\_update, SHA224\_final,

- SHA256 init, SHA256 update, SHA256 final.

- SHA384\_init, SHA384\_update, SHA384\_final.

- SHA512\_init, SHA512\_update, SHA512\_final.

These functions are not security relevant functions, i.e. they must not be used to hash security values like keys etc. There are implemented no countermeasures against side channel attacks. The TOE provides the functionality of hash computation if and only if the optional TORNADO™2MX2 Secure RSA/ECC library is delivered.

A True Random Number Generator (DTRNG) that fulfills the requirements of AIS 31, Class P2.

| 16 | The TOE | configur | ation is | summarized         | in table | ∘ 1 below∙ |

|----|---------|----------|----------|--------------------|----------|------------|

| 10 | THE TOE | comigai  | ation is | 5 dillillidi 12 cd | III tabi | e i bele   |

| Item Type              | Item                                                     | Version | Form of delivery             |

|------------------------|----------------------------------------------------------|---------|------------------------------|

| Hardware               | S3CT9P3 16-Bit RISC<br>Microcontroller for Smart<br>Card | 0       | Wafer or Module              |

| Software               | Test ROM Code                                            | 1.0     | Included in S3CT9P3 Test ROM |

| Software<br>(optional) | Secure RSA/ ECC Library                                  | 2.0     | Software Library             |

| Software               | DTRNG                                                    | 2.0     | Software Library             |

| Document               | API manual for the secure<br>RSA/ECC library             | 2.08    | Softcopy                     |

| Document               | DTRNG Application Note                                   | 1.3     | Softcopy                     |

| Document               | Hardware User's manual                                   | 1.21    | Softcopy                     |

| Document               | Security Application Note                                | 2.1     | Softcopy                     |

| Document               | Delivery Specification                                   | 1.0     | Softcopy                     |

| Document               | Architecture Reference:<br>SecuCalm16 CPU Core           | AR14    | Softcopy                     |

**Table 1 TOE Configuration**

17 Note: The TOE can be delivered without the RSA/ECC crypto library. In this case the TOE does not provide the Additional Specific Security Functionality RSA Cryptography and Elliptic Curve Cryptography (ECC) and Secure Hash Algorithm (SHA).

# 1.2.3 TOE Features

# CPU

• 16-bit SecuCalm core

## Memory

- 192K-byte Program Memory (ROM)

- 8K- byte Test ROM

- 12K-byte Data/Program Memory (EEPROM)

- 4K-byte Data Memory (RAM)

ELECTRONICS Version 1.2 Page 8 of 64

• 2.5K-byte Crypto Memory (Crypto RAM)

# **EEPROM Write Operations**

- Min. 500,000 write/erase cycles

- Data retention for min. 10 years

# **Triple DES**

- Built-in hardware Triple DES accelerator

- Circuit for resistance against SPA and DPA attacks

# **Abnormal Condition Detectors**

- Abnormal Voltage/Frequency/Light/Temperature detectors

- Power glitch detector (internal/external)

- Inner insulation removal detector

- Active shield removal detector

## Interrupts

Two interrupt sources and vectors (FIQ,IRQ)

#### Serial I/O Interface

UART for handling serial I/O interface in accordance with the ISO 7816 communication protocols

## **Reset and Power Down Mode**

Stop mode

# **Random Number Generator**

• A Digital True random number generator (DTRNG)

## **Memory Protection Unit**

The MPU allow the CPU to access memories through channels. Each channel can allow the access to a contiguous range of address.

# **Memory Encryption and Bus Scrambling**

Dynamic Data encryption for bus

## Timers

- 16-Bit Timer

- 20-bit Watchdog Timer

## **Clock Sources**

• External clock: 1 MHz-7.5 MHz

# **Operating Voltage Range**

• 1.62 V - 5.5 V

# **Operating Temperature**

- 25°C to 85°C

ECTRONICS Version 1.2 Page 9 of 64

# **Package**

- Wafer

- 8-pin COB (compliant with ISO 7816)

# 1.2.4 TOE Life cycle

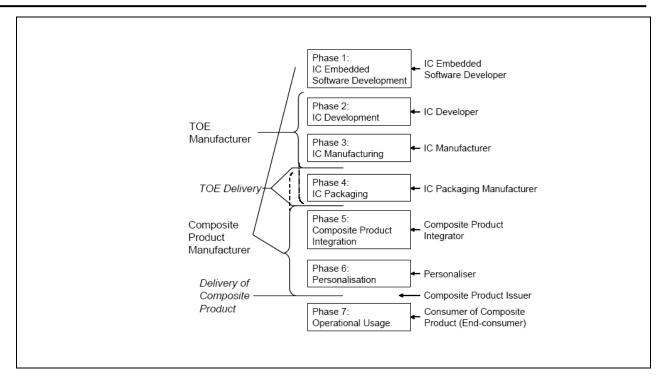

- The complex development and manufacturing processes of a Composite Product can be separated into seven distinct phases. The phases 2 and 3 of the Composite Product life cycle cover the IC development and production:

- IC Development (Phase 2):

- IC design,

- IC Dedicated Software development,

- the IC Manufacturing (Phase 3):

- integration and photomask fabrication,

- IC production,

- IC testing,

- preparation and

- Pre-personalisation if necessary

The Composite Product life cycle phase 4 can be included in the evaluation of the IC as an option:

- the IC Packaging (Phase 4):

- Security IC packaging (and testing),

- Pre-personalisation if necessary.

- 19 In addition, three important stages have to be considered in the Composite Product life cycle:

- Security IC Embedded Software Development (Phase 1),

- the Composite Product finishing process, preparation and shipping to the personalisation line for the Composite Product (Composite Product Integration Phase 5),

- the Composite Product personalisation and testing stage where the User Data is loaded into the Security IC's memory (Personalisation Phase 6),

- the Composite Product usage by its issuers and consumers (Operational Usage Phase 7) which may include loading and other management of applications in the field.

LECTRONICS Version 1.2 Page 10 of 64

Figure 2 Definition of "TOE Delivery" and responsible Parties

The Security IC Embedded Software is developed outside the TOE development in Phase 1. The TOE is developed in Phase 2 and produced in Phase 3. Then the TOE is delivered in form of wafers.

# 1.3 Interfaces of the TOE

- The physical interface of the TOE with the external environment is the entire surface of the IC

- The electrical interface of the TOE with the external environment is made of the chip's pads including the VDD, RESETB, XCLK, GND and IO1

- The data interface of the TOE is made of the Contact I/O pads.

- The software interface of the TOE with the hardware consists of Special Function Registers (SFR) and CPU instructions.

- The TRNG interface of the TOE is defined by the DTRNG library interface.

- The RSA interface of the TOE is defined by the RSA/ECC library interface (optional).

- The interface to the ECC and SHA calculations is defined from the RSA/ECC library interface (optional)

# 1.4 TOE Intended Usage

- 21 The TOE is dedicated to applications such as:

- Banking and finance applications for credit or debit cards, electronic purse (stored value cards) and electronic commerce.

- Network based transaction processing such a mobile phones (GSM SIM cards), pay TV (subscriber and pay-per-view cards), communication highways (Internet access and transaction processing).

- Transport and ticketing applications (access control cards).

- Governmental cards (ID cards, health cards, driving licenses).

- Multimedia applications and Digital Right Management protection.

TRONICS Version 1.2 Page 11 of 64

# 2 CONFORMANCE CLAIMS

- 22 This chapter 2 contains the following sections:

- 2.1 CC Conformance Claim

- 2.2 PP Claim

- 2.3 Package Claim

- 2.4 Conformance Claim Rationale

## 2.1 CC Conformance Claim

- 23 This Security target claims to be conformant to the Common Criteria version 3.1.

- Furthermore it claims to be CC Part 2 extended and CC Part 3 conformant. The extended Security Functional Requirements are defined in chapter 5.

- This *Security Target* has been built with the Common Criteria for Information Technology Security Evaluation; Version 3.1 which comprises

- [1] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and general model, Version 3.1, Revision 3, July 2009, CCMB-2009-07-001.

- [2] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 2: Security Functional Components, Version 3.1, Revision 3, July 2009, CCMB-2009-07-002.

- [3] Common Criteria, Common Criteria for Information Technology Security Evaluation, Part 3: Security Assurance Components, Version 3.1, Revision 3, July 2009, CCMB-2009-07-003.

- [4] Common Criteria, Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1, Revision 3, July 2009, CCMB-2009-07-004.

- 26 has been taken into account.

# 2.2 PP Claim

- 27 This Security Target is strict compliant to the Security IC Platform Protection Profile [5]. The Security IC Platform Protection Profile is registered and certified by the Bundesamt für Sicherheit in der Informationstechnik (BSI) under the reference BSI-PP-0035, Version 1.0, dated 15.06.2007.

- 28 This ST does not claim conformance to any other PP.

# 2.3 Package Claim

29 The assurance level for this Security Target is EAL5 augmented with AVA\_VAN.5 and ALC\_DVS.2.

#### 2.4 Conformance Claim Rationale

- This security target claims strict conformance only to one PP, the Security IC Platform Protection Profile [5].

- 31 The Evaluation Assurance Level (EAL) of the PP [5] is EAL 4 augmented with the assurance components ALC\_DVS.2 and AVA\_VAN.5. The Assurance Requirements of the TOE obtain the Evaluation Assurance Level 5 augmented with the assurance components ALC\_DVS.2 and AVA\_VAN.5 for the TOE.

CTRONICS Version 1.2 Page 12 of 64

- The Target of Evaluation (TOE) is a complete solution implementing a security integrated circuit (security IC) as defined in the PP ([5], section 1.3.1), so the TOE is consistent with the TOE type in the PP [5].

- The security problem definition of this security target is consistent with the statement of the security problem definition in the PP [5], as the security target claimed strict conformance to the PP [5]. Additional threats, organisational security policies and assumptions are introduced in chapter 3 of this ST, a rationale is given in chapter 4.4.

- The security objectives of this security target are consistent with the statement of the security objectives in the PP [5], as the security target claimed strict conformance to the PP [5]. Additional security objectives are added in chapter 4.1 of this ST, a rationale is given in chapter 4.4.

- The security requirements of this security target are consistent with the statement of the security requirements in the PP [5], as the security target claimed strict conformance to the PP [5]. Additional security requirements are added in chapter 6.1 of this ST, a rationale is given in chapter 6.3. All assignments and selections of the security functional requirements are done in the PP [5] and in this security target section 6.1.

LECTRONICS Version 1.2 Page 13 of 64

# 3 SECURITY PROBLEM DEFINITION

- 36 This chapter 3 contains the following sections:

- 3.1 Description of Assets

- 3.2 Threats

- 3.3 Organizational Security Policies

- 3.4 Assumptions

# 3.1 Description of Assets

# Assets regarding the Threats

- 37 The assets (related to standard functionality) to be protected are

- the User Data,

- the Security IC Embedded Software,

- the security services provided by the TOE for the Security IC Embedded Software.

- 38 The user (consumer) of the TOE places value upon the assets related to high-level security concerns:

- SC1 integrity of User Data and of the Security IC Embedded Software (while being executed/processed and while being stored in the TOE's memories),

- SC2 confidentiality of User Data and of the Security IC Embedded Software (while being processed and while being stored in the TOE's memories)

- SC3 correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- 39 The Security IC may not distinguish between User Data which are public known or kept confidential. Therefore the security IC shall protect the confidentiality and integrity of the User Data, unless the Security IC Embedded Software chooses to disclose or modify it.

- In particular integrity of the Security IC Embedded Software means that it is correctly being executed which includes the correct operation of the TOE's functionality. Though the Security IC Embedded Software (normally stored in the ROM) will in many cases not contain secret data or algorithms, it must be protected from being disclosed, since for instance knowledge of specific implementation details may assist an attacker.

- The Protection Profile requires the TOE to provide one security service: the generation of random numbers by means of a physical Random Number Generator. The Security Target may require additional security services. It is essential that the TOE ensures the correct operation of all security services provided by the TOE for the Security IC Embedded Software.

- 42 According to the Protection Profile there is the following high-level security concern related to security service:

- SC4 deficiency of random numbers.

- To be able to protect these assets the TOE shall protect its security functionality. Therefore critical information about the TOE shall be protected. Critical information includes:

- logical design data, physical design data, IC Dedicated Software, and configuration data,

- Initialisation Data and Pre-personalisation Data, specific development aids, test and characterisation related data, material for software development support, and photomasks.

ECTRONICS Version 1.2 Page 14 of 64

Such information and the ability to perform manipulations assist in threatening the above assets.

- Note that there are many ways to manipulate or disclose the User Data: (i) An attacker may manipulate the Security IC Embedded Software or the TOE. (ii) An attacker may cause malfunctions of the TOE or abuse Test Features provided by the TOE. Such attacks usually require design information of the TOE to be obtained. They pertain to all information about (i) the circuitry of the IC (hardware including the physical memories), (ii) the IC Dedicated Software with the parts IC Dedicated Test Software (if any) and IC Dedicated Support Software (if any), and (iii) the configuration data for the security functionality. The knowledge of this information enables or supports attacks on the assets. Therefore the TOE Manufacturer must ensure that the development and production of the TOE are secure so that no information is unintentionally made available for the operational phase of the TOE.

- The TOE Manufacturer must apply protection to support the security of the TOE. This not only pertains to the TOE but also to all information and material exchanged with the developer of the Security IC Embedded Software. This covers the Security IC Embedded Software itself if provided by the developer of the Security IC Embedded Software or any authentication data required to enable the download of software. This includes the delivery (exchange) procedures for Phase 1 and the Phases after TOE Delivery as far as they can be controlled by the TOE Manufacturer. These aspects enforce the usage of the supporting documents and the refinements of SAR defined in the protection profile.

- The information and material produced and/or processed by the TOE Manufacturer in the TOE development and production environment (Phases 2 up to TOE Delivery) can be grouped as follows:

- logical design data,

- physical design data,

- IC Dedicated Software, Security IC Embedded Software, Initialisation Data and Prepersonalisation Data,

- specific development aids,

- test and characterisation related data,

- material for software development support, and

- photomasks and products in any form

as long as they are generated, stored, or processed by the TOE Manufacturer.

# 3.2 Threats

- The following explanations help to understand the focus of the threats and objectives defined below. For example, certain attacks are only one step towards a disclosure of assets, others may directly lead to a compromise of the application security.

- Manipulation of data (which may comprise any data, including code, stored in or processed by the Security IC) means that an attacker is able to alter a meaningful block of data. This should be considered for the threats T.Malfunction, T.Phys-Manipulation and T.Abuse-Func.

- Manipulation of the TOE means that an attacker is able to deliberately deactivate or otherwise change the behaviour of a specific function in a manner which enables exploitation. This should be considered for the threat T.Malfunction, T.Phys-Manipulation and T.Abuse-Func.

- Disclosure of data (which may comprise any data, including code, stored in or processed by the Security IC) means that an attacker is realistically able to determine a meaningful block of data. This should be considered for the threats T.Leak-Inherent, T.Phys-Probing, T.Leak-Forced and T.Abuse-Func.

TRONICS Version 1.2 Page 15 of 64

- The cloning of the functional behaviour of the Security IC on its physical and command interface is the highest level security concern in the application context.

- The cloning of that functional behaviour requires to (i) develop a functional equivalent of the Security IC Embedded Software, (ii) disclose, interpret and employ the secret User Data stored in the TOE, and (iii) develop and build a functional equivalent of the Security IC using the input from the previous steps.

- The Security IC is a platform for the Security IC Embedded Software which ensures that especially the critical User Data are stored and processed in a secure way (refer to below). The Security IC Embedded Software must also ensure that critical User Data are treated as required in the application context. In addition, the personalisation process supported by the Security IC Embedded Software (and perhaps by the Security IC in addition) must be secure. This last step is beyond the scope of the Protection Profile. As a result the threat "cloning of the functional behaviour of the Security IC on its physical and command interface" is averted by the combination of measures which split into those being evaluated according to the Protection Profile (Security IC) and those being subject to the evaluation of the Security IC Embedded Software or Security IC and the corresponding personalisation process. Therefore, functional cloning is indirectly covered by the security concerns and threats described below.

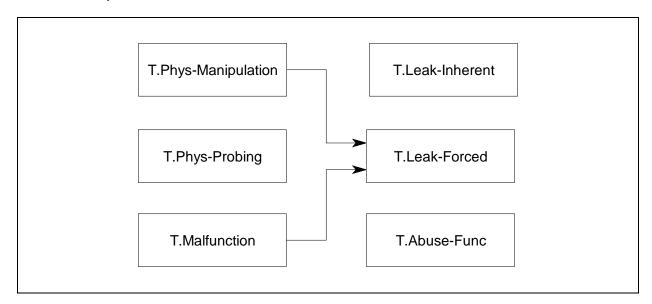

- The high-level security concerns are refined below by defining threats as required by the Common Criteria (refer to Figure 3). Note that manipulation of the TOE is only a means to threaten User Data or the Security IC Embedded Software and is not a success for the attacker in itself.

**Figure 3 Standard Threats**

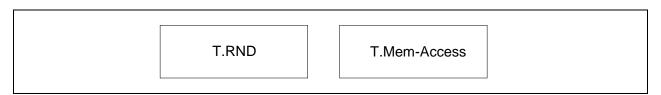

The high-level security concern related to security service is refined below by defining threats as required by the Common Criteria (refer to Figure 4).

Figure 4 Threats related to security service

The Security IC Embedded Software must contribute to averting the threats: At least it must not undermine the security provided by the TOE.

ECTRONICS Version 1.2 Page 16 of 64

- 54 The above security concerns are derived from considering the end-usage phase (Phase 7) since

- Phase 1 and the Phases from TOE Delivery up to the end of Phase 6 are covered by assumptions

- the development and production environment starting with Phase 2 up to TOE Delivery are covered by an organizational security policy.

- The TOE's countermeasures are designed to avert the threats described below. Nevertheless, they may be effective in earlier phases (Phases 4 to 6).

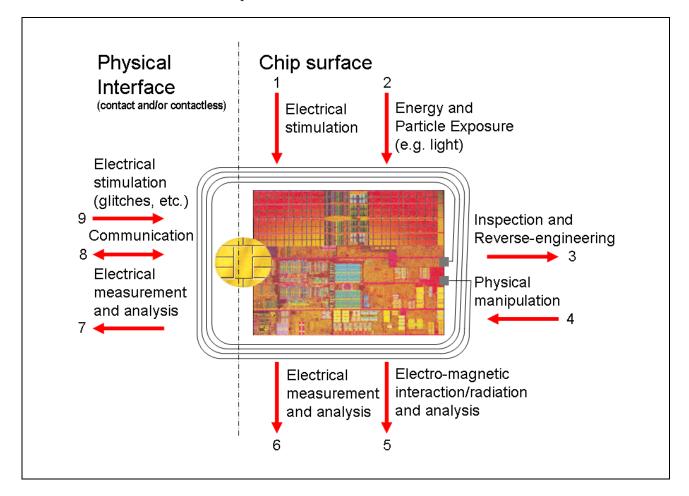

- The TOE is exposed to different types of influences or interactions with its outer world. Some of them may result from using the TOE only but others may also indicate an attack. The different types of influences or interactions are visualised in Figure 5. Due to the intended usage of the TOE all interactions are considered as possible.

Figure 5 Interactions between the TOE and its outer world

An interaction with the TOE can be done through the physical interfaces (Number 7 – 9 in Figure 5) which are realized using contacts interface. Influences or interactions with the TOE also occur through the chip surface (Number 1 – 6 in Figure 5). In Number 1 and 6 galvanic contacts are used. In Number 2 and 5 the influence (arrow directed to the chip) or the measurement (arrow starts from the chip) does not require a contact. Number 3 and 4 refer to specific situations where the TOE and its functional behaviour is not only influenced but definite changes are made by applying mechanical, chemical and other methods (such as 1, 2). Many attacks require a prior inspection and some reverse-engineering (Number 3). This demonstrates the basic building blocks of attacks. A practical attack will use a combination of these elements.

ECTRONICS Version 1.2 Page 17 of 64

## 3.2.1 Standard Threats

The TOE shall avert the threat "Inherent Information Leakage (T.Leak-Inherent)" as specified below.

T.Leak-Inherent Inherent Information Leakage

An attacker may exploit information which is leaked from the TOE during usage of the Security IC in order to disclose confidential data as part of the assets.

No direct contact with the Security IC internals is required here. Leakage may occur through emanations, variations in power consumption, I/O characteristics, clock frequency, or by changes in processing time requirements. One example is the Differential Power Analysis (DPA). This leakage may be interpreted as a covert channel transmission but is more closely related to measurement of operating parameters, which may be derived either from direct (contact) measurements (Numbers 6 and 7 in Figure 5) or measurement of emanations (Number 5 in Figure 5) and can then be related to the specific operation being performed.

59 The TOE shall avert the threat "Physical Probing (T.Phys-Probing)" as specified below.

T.Phys-Probing Physical Probing

An attacker may perform physical probing of the TOE in order (i) to disclose User Data, (ii) to disclose/reconstruct the Security IC Embedded Software or (iii) to disclose other critical information about the operation of the TOE.

Physical probing requires direct interaction with the Security IC internals (Numbers 5 and 6 in Figure 5). Techniques commonly employed in IC failure analysis and IC reverse engineering efforts may be used. Before that hardware security mechanisms and layout characteristics need to be identified (Number 3 in Figure 5). Determination of software design including treatment of User Data may also be a pre-requisite.

This pertains to "measurements" using galvanic contacts or any type of charge interaction whereas manipulations are considered under the threat "Physical Manipulation (T.Phys-Manipulation)". The threats "Inherent Information Leakage (T.Leak-Inherent)" and "Forced Information Leakage (T.Leak-Forced)" may use physical probing but require complex signal processing in addition.

The TOE shall avert the threat "Malfunction due to Environmental Stress (T.Malfunction)" as specified below.

T.Malfunction Malfunction due to Environmental Stress

An attacker may cause a malfunction of TSF or of the Security IC Embedded Software by applying environmental stress in order to (i) deactivate or modify security features or security services of the TOE or (ii) deactivate or modify functions of the Security IC Embedded Software. This may be achieved by operating the Security IC outside the normal operating conditions (Numbers 1, 2 and 9 in Figure 5).

The modification of security services of the TOE may e.g. affect the quality of random numbers provided by the random number generator up to undetected deactivation when the random number generator does not produce random numbers and the Security IC Embedded Software gets constant values. In another case errors are introduced in executing the Security IC Embedded Software. To exploit this, an attacker needs information about the functional operation, e.g. to introduce a temporary failure within a register used by the Security IC Embedded Software with light or a power glitch.

61 The TOE shall avert the threat "Physical Manipulation (T.Phys-Manipulation)" as specified below.

ECTRONICS Version 1.2 Page 18 of 64

T.Phys-Manipulation Physical Manipulation

An attacker may physically modify the Security IC in order to (i) modify security features or security services of the TOE, (ii) modify functions of the Security IC Embedded Software or (iii) to modify User Data.

The modification may be achieved through techniques commonly employed in IC failure analysis (Numbers 1, 2 and 4 in Figure 8) and IC reverse engineering efforts (Number 3 in Figure 8). The modification may result in the deactivation of a security feature. Before that hardware security mechanisms and layout characteristics need to be identified. Determination of software design including treatment of User Data may also be a pre-requisite. Changes of circuitry or data can be permanent or temporary.

In contrast to malfunctions (refer to T.Malfunction) the attacker requires gathering significant knowledge about the TOE's internal construction here (Number 3 in Figure 5).

62 The TOE shall avert the threat "Forced Information Leakage (T.Leak-Forced)" as specified below:

T.Leak-Forced Forced Information Leakage

An attacker may exploit information which is leaked from the TOE during usage of the Security IC in order to disclose confidential data as part of the assets even if the information leakage is not inherent but caused by the attacker.

This threat pertains to attacks where methods described in "Malfunction due to Environmental Stress" (refer to T.Malfunction) and/or "Physical Manipulation" (refer to T.Phys-Manipulation) are used to cause leakage from signals (Numbers 5, 6, 7 and 8 in Figure 5) which normally do not contain significant information about secrets.

63 The TOE shall avert the threat "Abuse of Functionality (T.Abuse-Func)" as specified below.

T.Abuse-Func Abuse of Functionality

An attacker may use functions of the TOE which may not be used after TOE Delivery in order to (i) disclose or manipulate User Data, (ii) manipulate (explore, bypass, deactivate or change) security services of the TOE or (iii) manipulate (explore, bypass, deactivate or change) functions of the Security IC Embedded Software or (iv) enable an attack disclosing or manipulating the User Data or the Security IC Embedded Software.

# 3.2.2 Threats related to security services

64 The TOE shall avert the threat "Deficiency of Random Numbers (T.RND)" as specified below.

T.RND Deficiency of Random Numbers

An attacker may predict or obtain information about random numbers generated by the TOE for instance because of a lack of entropy of the random numbers provided.

An attacker may gather information about the produced random numbers which might be a problem because they may be used for instance to generate cryptographic keys.

Here the attacker is expected to take advantage of statistical properties of the random numbers generated by the TOE without specific knowledge about

Version 1.2 Page 19 of 64

the TOE's generator. Malfunctions or premature ageing are also considered which may assist in getting information about random numbers.

# 3.2.3 Threats related to additional TOE Specific Functionality

The TOE shall avert the additional threat "Memory Access Violation (T.Mem-Access)" as specified below.

T.Mem-Access

Memory Access Violation

Parts of the Smartcard Embedded Software may cause security violations by accidentally or deliberately accessing restricted data (which may include code). Any restrictions are defined by the security policy of the specific application context and must be implemented by the Smartcard Embedded Software.

# 3.3 Organizational Security Policies

66 The following Figure 6 shows the policies applied in this Security Target.

P.Process-TOE P.Add-Functions

Figure 6 Policies

The IC Developer / Manufacturer must apply the policy "Protection during TOE Development and Production (P.Process-TOE)" as specified below.

P.Process-TOE

Protection during TOE Development and Production

An accurate identification must be established for the TOE. This requires that each instantiation of the TOE carries this unique identification.

- The accurate identification is introduced at the end of the production test in phase 3. Therefore the production environment must support this unique identification.

- The information and material produced and/or processed by the TOE Manufacturer in the TOE development and production environment (Phases 2 up to TOE Delivery) can be grouped as follows:

- logical design data,

- physical design data,

- IC Dedicated Software, Security IC Embedded Software, Initialisation Data and Prepersonalisation Data,

- specific development aids,

- test and characterisation related data,

- material for software development support, and

- photomasks and products in any form

as long as they are generated, stored, or processed by the TOE Manufacturer.

The TOE provides specific security functionality which can be used by the Smartcard Embedded Software. In the following specific security functionality is listed which is not derived from threats identified for the TOE's environment because it can only be decided in the context of the smartcard

ECTRONICS Version 1.2 Page 20 of 64

application, against which threats the Smartcard Embedded Software will use the specific security functionality.

71 The IC Developer / Manufacturer must apply the policy "Additional Specific Security Functionality (P.Add-Functions)" as specified below.

P.Add-Functions

Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Smartcard Embedded Software:

- Triple Data Encryption Standard (3DES)

- RSA public key asymmetric cryptography (optional)

- Elliptic Curve Cryptography (ECC) and Secure Hash Algorithm (SHA) (optional)

Note: The TOE can be delivered without the RSA/ECC crypto library. In this case the TOE does not provide the Additional Specific Security Functionality RSA Cryptography and Elliptic Curve Cryptography (ECC) and Secure Hash Algorithm (SHA).

# 3.4 Assumptions

- The intended usage of the TOE is twofold, depending on the Life Cycle Phase: (i) The Security IC Embedded Software developer uses it as a platform for the Security IC software being developed. The Composite Product Manufacturer (and the consumer) uses it as a part of the Security IC. The Composite Product is used in a terminal which supplies the Security IC (with power and clock) and (at least) mediates the communication with the Security IC Embedded Software.

- Before being delivered to the consumer the TOE is packaged. Many attacks require the TOE to be removed from the carrier. Though this extra step adds difficulties for the attacker no specific assumptions are made here regarding the package.

- Appropriate "Protection during Packaging, Finishing and Personalisation (A.Process-Sec-IC)" must be ensured after TOE Delivery up to the end of Phase 6, as well as during the delivery to Phase 7 as specified below.

A.Process-Sec-IC

Protection during Packaging, Finishing and Personalisation

It is assumed that security procedures are used after delivery of the TOE by the TOE Manufacturer up to delivery to the consumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorized use).

This means that the Phases after TOE Delivery are assumed to be protected appropriately.

- The information and material produced and/or processed by the Security IC Embedded Software Developer in Phase 1 and by the Composite Product Manufacturer can be grouped as follows:

- the Security IC Embedded Software including specifications, implementation and related documentation,

- pre-personalisation and personalisation data including specifications of formats and memory areas, test related data,

- the User Data and related documentation, and

LECTRONICS Version 1.2 Page 21 of 64

material for software development support

as long as they are not under the control of the TOE Manufacturer. Details must be defined in the Protection Profile or Security Target for the evaluation of the Security IC Embedded Software and/or Security IC.

The developer of the Security IC Embedded Software must ensure the appropriate "Usage of Hardware Platform (A.Plat-Appl)" while developing this software in Phase 1 as specified below.

A.Plat-Appl

Usage of Hardware Platform

The Security IC Embedded Software is designed so that the requirements from the following documents are met: (i) TOE guidance documents (refer to the Common Criteria assurance class AGD) such as the hardware data sheet, and the hardware application notes, and (ii) findings of the TOE evaluation reports relevant for the Security IC Embedded Software as documented in the certification report.

- Note that particular requirements for the Security IC Embedded Software are often not clear before considering a specific attack scenario during vulnerability analysis of the Security IC (AVA\_VAN). A summary of such results is provided in the document "ETR for composite evaluation" (ETR-COMP). This document can be provided for the evaluation of the composite product. The ETR-COMP may also include guidance for additional tests being required for the combination of hardware and software. The TOE evaluation must be completed before evaluation of the Security IC Embedded Software can be completed. The TOE evaluation can be conducted before and independent from the evaluation of the Security IC Embedded Software.

- 78 The developer of the Security IC Embedded Software must ensure the appropriate "Treatment of User Data (A.Resp-Appl)" while developing this software in Phase 1 as specified below.

A.Resp-Appl

Treatment of User Data

All User Data are owned by Security IC Embedded Software. Therefore, it must be assumed that security relevant User Data (especially cryptographic keys) are treated by the Security IC Embedded Software as defined for its specific application context.

The application context specifies how the User Data shall be handled and protected. The evaluation of the Security IC according to this Protection Profile is conducted on generalized application context. The concrete requirements for the Security IC Embedded Software shall be defined in the Protection Profile respective Security Target for the Security IC Embedded Software. The Security IC cannot prevent any compromise or modification of User Data by malicious Security IC Embedded Software. The assumption A.Resp-Appl ensures that the Security IC Embedded Software follows the security rules of the application context. Examples are given in Section 7.2.1, all being directly related to and covered by A.Resp-Appl.

79 The developer of the Smartcard Embedded Software must ensure the appropriate "Usage of Keydependent Functions (A.Key-Function)" while developing this software in Phase 1 as specified below.

A.Key-Function

Usage of Key-dependent Functions

Key-dependent functions (if any) shall be implemented in the Smartcard Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

Note that here the routines which may compromise keys when being executed are part of the Smartcard Embedded Software. In contrast to this the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines which are part of the TOE and (ii) the processing of User Data including cryptographic keys.

ELECTRONICS Version 1.2 Page 22 of 64

# **4 SECURITY OBJECTIVES**

- 80 This chapter Security Objectives contains the following sections:

- 4.1 Security Objectives for the TOE

- 4.2 Security Objectives for the IC Embedded Software development Environment

- 4.3 Security Objectives for the operational Environment

- 4.4 Security Objectives Rationale

# 4.1 Security objectives for the TOE

- 81 According to the Protection Profile [5] there are the following standard high-level security goals:

- SG1 maintain the integrity of User Data and of the Security IC Embedded Software (when being executed/processed and when being stored in the TOE's memories) as well as

- SG2 maintain the confidentiality of User Data and of the Security IC Embedded Software (when being processed and when being stored in the TOE's memories).

The Security IC may not distinguish between User Data which are public known or kept confidential. Therefore the security IC shall protect the confidentiality and integrity of the User Data, unless the Security IC Embedded Software chooses to disclose or modify it.

In particular integrity of the Security IC Embedded Software means that it is correctly being executed which includes the correct operation of the TOE's functionality. Though the Security IC Embedded Software (normally stored in the ROM) will in many cases not contain secret data or algorithms, it must be protected from being disclosed, since for instance knowledge of specific implementation details may assist an attacker.

- SG3 maintain the correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- SG4 provide random numbers.

- These standard high-level security goals are refined below by defining security objectives as required by the *Common Criteria*. Note that the integrity of the TOE is a mean to reach these objectives.

# **Standard Security Objectives**

83 The TOE shall provide "Protection against Inherent Information Leakage (O.Leak-Inherent)" as specified below.

O.Leak-Inherent

Protection against Inherent Information Leakage

The TOE must provide protection against disclosure of confidential data (User Data or TSF data) stored and/or processed in the Smartcard IC

- by measurement and analysis of the shape and amplitude of signals (for example on the power, clock, or I/O lines) and

- by measurement and analysis of the time between events found by measuring signals (for instance on the power, clock, or I/O lines).

This objective pertains to measurements with subsequent complex signal processing whereas O.Phys-Probing is about direct measurements on elements on the chip surface. Details correspond to an analysis of attack scenarios which is not given here.

Version 1.2 Page 23 of 64

The TOE shall provide "Protection against Physical Probing (O.Phys-Probing)" as specified below.

O.Phys-Probing Protection against Physical Probing

The TOE must provide protection against disclosure of User Data, against the disclosure/reconstruction of the Smartcard Embedded Software or against the disclosure of other critical operational information. This includes protection against

- measuring through galvanic contacts which is direct physical probing on the chips surface except on pads being bonded (using standard tools for measuring voltage and current) or

- measuring not using galvanic contacts but other types of physical interaction between charges (using tools used in solid-state physics research and IC failure analysis)

with a prior

reverse-engineering to understand the design and its properties and functions.

The TOE must be designed and fabricated so that it requires a high combination of complex equipment, knowledge, skill, and time to be able to derive detailed design information or other information which could be used to compromise security through such a physical attack.

85 The TOE shall provide "Protection against Malfunctions (O.Malfunction)" as specified below.

O.Malfunction

Protection against Malfunctions

The TOE must ensure its correct operation.

The TOE must prevent its operation outside the normal operating conditions where reliability and secure operation has not been proven or tested. This is to prevent errors. The environmental conditions may include voltage, clock frequency, temperature, or external energy fields.

Remark: A malfunction of the TOE may also be caused using a direct interaction with elements on the chip surface. This is considered as being a manipulation (refer to the objective O.Phys-Manipulation) provided that detailed knowledge about the TOE's internal construction is required and the attack is performed in a controlled manner.

The TOE shall provide "Protection against Physical Manipulation (O.Phys-Manipulation)" as specified below.

O.Phys-Manipulation Protection against Physical Manipulation

The TOE must provide protection against manipulation of the TOE (including its software and TSF data), the Smartcard Embedded Software and the User Data. This includes protection against

- reverse-engineering (understanding the design and its properties and functions),

- manipulation of the hardware and any data, as well as

ECTRONICS Version 1.2 Page 24 of 64

• controlled manipulation of memory contents (User Data).

The TOE must be designed and fabricated so that it requires a high combination of complex equipment, knowledge, skill, and time to be able to derive detailed design information or other information which could be used to compromise security through such a physical attack.

87 The TOE shall provide "Protection against Forced Information Leakage (O.Leak-Forced)" as specified below:

O.Leak-Forced

Protection against Forced Information Leakage

The Security IC must be protected against disclosure of confidential data processed in the Security IC (using methods as described under O.Leak-Inherent) even if the information leakage is not inherent but caused by the attacker

- by forcing a malfunction (refer to "Protection against Malfunction due to Environmental Stress (O.Malfunction)" and/or

- by a physical manipulation (refer to "Protection against Physical Manipulation (O.Phys-Manipulation)".

If this is not the case, signals which normally do not contain significant information about secrets could become an information channel for a leakage attack.

88 The TOE shall provide "Protection against Abuse of Functionality (O.Abuse-Func)" as specified below.

O.Abuse-Func

Protection against Abuse of Functionality

The TOE must prevent that functions of the TOE which may not be used after TOE Delivery can be abused in order (i) to disclose critical User Data, (ii) to manipulate critical User Data of the Smartcard Embedded Software, (iii) to manipulate Soft-coded Smartcard Embedded Software or (iv) bypass, deactivate, change or explore security features or functions of the TOE. Details depend, for instance, on the capabilities of the Test Features provided by the IC Dedicated Test Software which are not specified here.

89 The TOE shall provide "TOE Identification (O.Identification)" as specified below:

O.Identification

**TOE Identification**

The TOE must provide means to store Initialization Data and Prepersonalization Data in its non-volatile memory. The Initialization Data (or parts of them) are used for TOE identification.

# Security Objectives related to Specific Functionality (referring to SC4)

90 The TOE shall provide "Random Numbers (O.RND)" as specified below.

O.RND

Random Numbers

The TOE will ensure the cryptographic quality of random number generation. For instance random numbers shall not be predictable and shall have sufficient entropy.

ECTRONICS Version 1.2 Page 25 of 64

The TOE will ensure that no information about the produced random numbers is available to an attacker since they might be used for instance to generate cryptographic keys.

# **Security Objectives for Added Function**

The TOE shall provide "Additional Specific Security Functionality (O.Add-Functions)" as specified below.

O.Add-Functions

Additional Specific Security Functionality

The TOE must provide the following specific security functionality to the Smartcard Embedded Software:

- Triple Data Encryption Standard (3DES)

- RSA public key asymmetric cryptography (optional)

- Elliptic Curve Cryptography (ECC) and Secure Hash Algorithm (SHA).(optional)

Note: The TOE can be delivered without the RSA/ECC crypto library. In this case the TOE does not provide the Additional Specific Security Functionality RSA Cryptography and Elliptic Curve Cryptography (ECC) and Secure Hash Algorithm (SHA).

92 The TOE shall provide "Area based Memory Access Control (O.Mem-Access)" as specified below.

O.Mem-Access

Area based Memory Access Control

The TOE must provide the Smartcard Embedded Software with the capability to define restricted access memory areas. The TOE must then enforce the partitioning of such memory areas so that access of software to memory areas is controlled as required, for example, in a multi-application environment.

# 4.2 Security Objectives for the Security IC Embedded software development Environment

# Phase 1

The Security IC Embedded Software shall provide "Usage of Hardware Platform (OE.Plat-Appl)" as specified below.

OE.Plat-Appl

Usage of Hardware Platform

To ensure that the TOE is used in a secure manner the Security IC Embedded Software shall be designed so that the requirements from the following documents are met: (i) hardware data sheet for the TOE, (ii) data sheet of the IC Dedicated Software of the TOE, (iii) TOE application notes, other guidance documents, and (iv) findings of the TOE evaluation reports relevant for the Security IC Embedded Software as referenced in the certification report.

The Security IC Embedded Software shall provide "Treatment of User Data (OE.Resp-Appl)" as specified below.

OE.Resp-Appl Treatment of User Data

S Version 1.2 Page 26 of 64

Security relevant User Data (especially cryptographic keys) are treated by the Smartcard Embedded Software as required by the security needs of the specific application context.

For example the Smartcard Embedded Software will not disclose security relevant user data to unauthorized users or processes when communicating with a terminal.

# 4.2.1 Clarification of "Usage of Hardware Platform (OE.Plat-Appl)"

- Regarding the cryptographic services this objective of the environment has to be clarified. The TOE supports cipher schemes as additional specific security functionality. If required the Smartcard Embedded Software shall use these cryptographic services of the TOE and their interface as specified. When key-dependent functions implemented in the Smartcard Embedded Software are just being executed, the Smartcard Embedded Software must provide protection against disclosure of confidential data (User Data) stored and/or processed in the TOE by using the methods described under "Inherent Information Leakage (T.Leak-Inherent)" and "Forced Information Leakage (T.Leak-Forced)".

- Regarding the area based access control this objective of the environment has to be clarified. For the separation of different applications the Smartcard Embedded Software (Operating System) may implement a memory management scheme based upon security mechanisms of the TOE.

- 97 For the separation of different applications the Smartcard Embedded Software may implement a memory management scheme based upon security mechanisms of the TOE as required by the security policy defined for the specific application context.

# 4.2.2 Clarification of "Treatment of User Data (OE.Resp-Appl)"

- 98 Regarding the cryptographic services this objective of the environment has to be clarified. By definition cipher or plain text data and cryptographic keys are User Data. The Smartcard Embedded Software shall treat these data appropriately, use only proper secret keys (chosen from a large key space) as input for the cryptographic function of the TOE and use keys and functions appropriately in order to ensure the strength of cryptographic operation.

- This means that keys are treated as confidential as soon as they are generated. The keys must be unique with a very high probability, as well as cryptographically strong. For example, it must be ensured that it is beyond practicality to derive the private key from a public key if asymmetric algorithms are used. If keys are imported into the TOE and/or derived from other keys, quality and confidentiality must be maintained. This implies that appropriate key management has to be realised in the environment.

- 100 Regarding the area based access control this objective of the environment has to be clarified. The treatment of User Data is also required when a multi-application operating system is implemented as part of the Smartcard Embedded Software on the TOE. In this case the multi-application operating system should not disclose security relevant user data of one application to another application when it is processed or stored on the TOE.

- 101 The treatment of User Data is still required when a multi-application operating system is implemented as part of the Smartcard Embedded Software on the TOE. In this case the multi-application operating system should not disclose security relevant user data of one application to another application when it is processed or stored on the TOE.

# 4.3 Security objectives for the operational Environment

# TOE Delivery up to the end of Phase 6

Appropriate "Protection during Packaging, Finishing and Personalisation (OE.Process-Sec-IC)" must be ensured after TOE Delivery up to the end of Phases 6, as well as during the delivery to Phase 7 as specified below.

LECTRONICS Version 1.2 Page 27 of 64

OE.Process-Sec-IC

Protection during composite product manufacturing

Security procedures shall be used after TOE Delivery up to delivery to the "consumer" to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorized use).

This means that Phases after TOE Delivery up to the end of Phase 6 must be protected appropriately.

# 4.3.1 Clarification of "Protection during Composite product manufacturing (OE.Process-Sec-IC)"

- The protection during packaging, finishing and personalization includes also the personalization process and the personalization data during Phase 4, Phase 5 and Phase 6.

- Since OE.Process-Sec-IC requires the Composite Product Manufacturer to implement those measures assumed in A.Process-Sec-IC, the assumption is covered by this objective.

# 4.4 Security Objectives Rationale

Table 3 below gives an overview, how the assumptions, threats, and organisational security policies are addressed by the objectives. The text following after the table justifies this in detail.

| Assumption, Threat or<br>Organizational Security<br>Policy | Security Objective           | Notes                           |

|------------------------------------------------------------|------------------------------|---------------------------------|

| A.Plat-Appl                                                | OE.Plat-Appl                 | Phase 1                         |

| A.Resp-Appl                                                | OE.Resp-Appl                 | Phase 1                         |

| P.Process-TOE                                              | O.Identification             | Phase 2 – 3<br>optional Phase 4 |

| A.Process-Sec-IC                                           | OE.Process-Sec-IC            | Phase 5 – 6<br>optional Phase 4 |

| T.Leak-Inherent                                            | O.Leak-Inherent              |                                 |

| T.Phys-Probing                                             | O.Phys-Probing               |                                 |

| T.Malfunction                                              | O.Malfunction                |                                 |

| T.Phys-Manipulation                                        | O.Phys-Manipulation          |                                 |

| T.Leak-Forced                                              | O.Leak-Forced                |                                 |

| T.Abuse-Func                                               | O.Abuse-Func                 |                                 |

| T.RND                                                      | O.RND                        |                                 |

| T.Mem-Access                                               | O.Mem-Access                 |                                 |

| P.Add-Functions                                            | O.Add-Functions              |                                 |

| A.Key-Function                                             | OE.Plat-Appl<br>OE.Resp-Appl |                                 |

Table 3 Security Objectives versus Assumptions, Threats or Policies

- 106 The justification related to the assumption "Usage of Hardware Platform (A.Plat-Appl)" is as follows:

- 107 Since OE.Plat-Appl requires the Smartcard Embedded Software developer to implement those measures assumed in A.Plat-Appl, the assumption is covered by the objective.

Version 1.2 Page 28 of 64

- 108 The justification related to the assumption "Treatment of User Data (A.Resp-Appl)" is as follows:

- 109 Since OE.Resp-Appl requires the developer of the Smartcard Embedded Software to implement measures as assumed in A.Resp-Appl, the assumption is covered by the objective.

- The justification related to the organisational security policy "Protection during TOE Development and Production (P.Process-TOE)" is as follows:

- O.Identification requires that the TOE has to support the possibility of a unique identification. The unique identification can be stored on the TOE. Since the unique identification is generated by the production environment the production environment must support the integrity of the generated unique identification. The technical and organisational security measures that ensure the security of the development environment and production environment are evaluated based on the assurance measures that are part of the evaluation. For a list of material produced and processed by the TOE Manufacturer refer to paragraph 43 (page 15). All listed items and the associated development and production environments are subject of the evaluation. Therefore, the organisational security policy P.Process-TOE is covered by this objective, as far as organisational measures are concerned.

- The justification related to the assumption "Protection during Packaging, Finishing and Personalisation (A.Process-Sec-IC)" is as follows:

- Since OE.Process-Sec-IC requires the Composite Product Manufacturer to implement those measures assumed in A.Process-Sec-IC, the assumption is covered by this objective.

- The justification related to the threats "Inherent Information Leakage (T.Leak-Inherent)", "Physical Probing (T.Phys-Probing)", "Malfunction due to Environmental Stress (T.Malfunction)", "Physical Manipulation (T.Phys-Manipulation)", "Forced Information Leakage (T.Leak-Forced)", "Abuse of Functionality (T.Abuse-Func)" and "Deficiency of Random Numbers (T.RND)" is as follows:

- 115 For all threats the corresponding objectives are stated in a way, which directly corresponds to the description of the threat. It is clear from the description of each objective, that the corresponding threat is removed if the objective is valid. More specifically, in every case the ability to use the attack method successfully is countered, if the objective holds.

- 116 The justification related to the threat "Memory Access Violation (T.Mem-Access)" is as follows:

- 117 According to O.Mem-Access the TOE must enforce the partitioning of memory areas so that access of software to memory areas is controlled. Any restrictions are to be defined by the Smartcard Embedded Software. Thereby security violations caused by accidental or deliberate access to restricted data (which may include code) can be prevented (refer to T.Mem-Access). The threat T.Mem-Access is therefore removed if the objective is met.

- The clarification of "Usage of Hardware Platform (OE.Plat-Appl)" makes clear that it is up to the Smartcard Embedded Software to implement the memory management scheme by appropriately administrating the TSF. This is also expressed both in T.Mem-Access and O.Mem-Access. The TOE shall provide access control functions as a means to be used by the Smartcard Embedded Software. This is further emphasised by the clarification of "Treatment of User Data (OE.Resp-Appl)" which reminds that the Smartcard Embedded Software must not undermine the restrictions it defines. Therefore, the clarifications contribute to the coverage of the threat T.Mem-Access.

- The justification related to the security objective "Additional Specific Security Functionality (O.Add-Functions)" is as follows:

- Since O.Add-Functions requires the TOE to implement exactly the same specific security functionality as required by P.Add-Functions, the organisational security policy is covered by the objective.

- 121 Nevertheless the security objectives O.Leak-Inherent, O.Phys-Probing, O.Malfunction, O.Phys-Manipulation and O.Leak-Forced define how to implement the specific security functionality required by P.Add-Functions. (Note that these objectives support that the specific security functionality is provided in a secure way as expected from P.Add-Functions.) Especially O.Leak-Inherent and O.Leak-Forced refer to the protection of confidential data (User Data or TSF data) in general. User Data are also processed by the specific security functionality required by P.Add-Functions.

ECTRONICS Version 1.2 Page 29 of 64

- 122 Compared to Smartcard IC Platform Protection Profile a clarification has been made for the security objective "Usage of Hardware Platform (OE.Plat-Appl)": If required the Smartcard Embedded Software shall use these cryptographic services of the TOE and their interface as specified. In addition, the Smartcard Embedded Software must implement functions which perform operations on keys (if any) in such a manner that they do not disclose information about confidential data. The non disclosure due to leakage A.Key-Function attacks is included in this objective OE.Plat-Appl. This addition ensures that the assumption A.Plat-Appl is still covered by the objective OE.Plat-Appl although additional functions are being supported according to O.Add-Functions.

- 123 Compared to Smartcard IC Platform Protection Profile a clarification has been made for the security objective "Treatment of User Data (OE.Resp-Appl)": By definition cipher or plain text data and cryptographic keys are User Data. So, the Smartcard Embedded Software will protect such data if required and use keys and functions appropriately in order to ensure the strength of cryptographic operation. Quality and confidentiality must be maintained for keys that are imported and/or derived from other keys. This implies that appropriate key management has to be realised in the environment. That is expressed by the assumption A.Key Function which is covered from OE.Resp-Appl. These measures make sure that the assumption A.Resp-Appl is still covered by the security objective OE.Resp-Appl although additional functions are being supported according to P.Add-Functions.

- The justification of the additional policy and the additional assumption show that they do not contradict to the rationale already given in the Protection Profile for the assumptions, policy and threats defined there.

Version 1.2 Page 30 of 64

# 5 EXTENDED COMPONENTS DEFINITION

- 125 This chapter 5 Extended Components Definition contains the following sections:

- 5.1 Definition of the family FCS\_RNG

- 5.2 Definition of the Family FMT\_LIM

- 5.3 Definition of the Family FAU\_SAS

# 5.1 Definition of the Family FCS\_RNG

To define the IT security functional requirements of the TOE an additional family (FCS\_RNG) of the Class FCS (cryptographic support) is defined here. This family describes the functional requirements for random number generation used for cryptographic purposes.

# FCS\_RNG Generation of random numbers

Family behaviour

This family defines quality requirements for the generation of random numbers which are intended to be use for cryptographic purposes.

Component levelling:

FCS\_RNG Generation of random numbers 1

FCS\_RNG.1 Generation of random numbers requires that random numbers meet a

defined quality metric.

Management: FCS\_RNG.1

There are no management activities foreseen.

Audit: FCS\_RNG.1

There are no actions defined to be auditable.

FCS\_RNG.1 Random number generation

Hierarchical to: No other components.

Dependencies: No dependencies.

FCS\_RNG.1.1 The TSF shall provide a [selection: physical, non-physical true, deterministic,

hybrid] random number generator that implements: [assignment: list of

security capabilities].

FCS\_RNG.1.2 The TSF shall provide random numbers that meet [assignment: a defined

quality metric].

TRONICS Version 1.2 Page 31 of 64

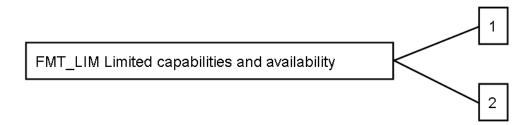

# 5.2 Definition of the Family FMT\_LIM

- To define the IT security functional requirements of the TOE an additional family (FMT\_LIM) of the Class FMT (Security Management) is defined here. This family describes the functional requirements for the Test Features of the TOE. The new functional requirements were defined in the class FMT because this class addresses the management of functions of the TSF. The examples of the technical mechanism used in the TOE appropriate to address the specific issues of preventing the abuse of functions by limiting the capabilities of the functions and by limiting their availability.

- 128 The family "Limited capabilities and availability (FMT\_LIM)" is specified as follows.

# FMT\_LIM Limited capabilities and availability

Family behavior

This family defines requirements that limit the capabilities and availability of functions in a combined manner. Note that FDP\_ACF restricts the access to functions whereas the component Limited Capability of this family requires the functions themselves to be designed in a specific manner.

Component levelling:

FMT\_LIM.1 Limited capabilities require that the TSF is built to provide only the

capabilities (perform action, gather information) necessary for its genuine

purpose.

FMT LIM.2 Limited availability requires that the TSF restrict the use of functions (refer

to Limited capabilities (FMT\_LIM.1)). This can be achieved, for instance, by removing or by disabling functions in a specific phase of the TOE's life-cycle.

Management: FMT\_LIM.1, FMT\_LIM.2

There are no management activities foreseen.

Audit: FMT\_LIM.1, FMT\_LIM.2

There are no actions defined to be auditable.

129 The TOE Functional Requirement "Limited capabilities (FMT\_LIM.1)" is specified as follows.

FMT\_LIM.1 Limited capabilities

Hierarchical to: No other components.

FMT\_LIM.1.1 The TSF shall be designed and implemented in a manner that limits their

capabilities so that in conjunction with "Limited availability (FMT\_LIM.2)" the following policy is enforced [assignment: Limited capability and

availability policy].

LECTRONICS Version 1.2 Page 32 of 64

CROW V SECURITY TARGET PUBLIC

Dependencies: FMT\_LIM.2 Limited availability.

130 The TOE Functional Requirement "Limited availability (FMT\_LIM.2)" is specified as follows.

FMT\_LIM.2 Limited availability

Hierarchical to: No other components.

FMT\_LIM.2.1 The TSF shall be designed in a manner that limits their availability so that in

conjunction with "Limited capabilities (FMT\_LIM.1)" the following policy is