**Security Target Lite**

M5073 G11

**Including optional Software Libraries** RSA - EC - SHA-2 - Toolbox

Common Criteria CCv3.1 EAL6 augmented (EAL6+)

Resistance to attackers with HIGH attack potential

Document version 0.6 as of 2015-10-30

Hans-Ulrich Buchmüller

# Chipcard & Security

Edition 2015-10-30

Published by Infineon Technologies AG, 81726 Munich, Germany.

© 2015 Infineon Technologies AG

All Rights Reserved.

## Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Security Target Lite 2 2015-10-30

## Miscellaneous

The term "Mifare" in this document is only used as an indicator of product compatibility to the corresponding established technology. This applies to the entire document wherever the term is used.

## **Trademarks of Infineon Technologies AG**

AURIX™, C166™, Canpak™, Cipos™, Coolgan™, Coolmos™, Coolset™, Coolsic™, Corecontrol™, Crossave™, Dave™, Di-Pol™, DrBlade™, Easypim™, Econobridge™, Econodual™, Econopack™, Econopim™, Eicedriver™, eupec™, Fcos™, Hitfet™, Hybridpack™, Infineon™, Isoface™, Isopack™, i-Wafer™, Mipaq™, Modstack™, my-d™, Novalithic™, Omnitune™, Optiga™, Optimos™, Origa™, Powercode™, Primarion™, Primapack™, Primastack™, Profet™, Prosil™, Rasic™, Real3™, Reversave™, Satric™, Sieget™, Sipmos™, Smartlewis™, Solid Flash™, Spoc™, Tempfet™, thinq!™, Trenchstop™, Tricore™.

Trademarks updated August 2015

#### **Other Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Security Target Lite 3 2015-10-30

## **Revision History**

| Date       | ate Version Change Description                  |                                                 |

|------------|-------------------------------------------------|-------------------------------------------------|

| 2015-05-13 | 0.1                                             | Initial version                                 |

| 2015-05-20 | 0.2                                             | User Guidance versions update                   |

| 2015-05-28 | 0.3                                             | Editorial changes consider 0951_OR_IA_150520_v1 |

| 2015-07-10 | 07-10 0.4 Update of firmware identifier version |                                                 |

| 2015-08-21 | 0.5                                             | Update of user guidance references              |

| 2015-10-30 | 0.6                                             | Editorial changes in chapter 1.1                |

## **Table of Contents**

| 1 | SEC  | CURITY TARGET INTRODUCTION (ASE_INT)               | <u>.</u> |

|---|------|----------------------------------------------------|----------|

|   | 1.1  | SECURITY TARGET AND TARGET OF EVALUATION REFER     | ENCE     |

|   | 1.2  | TARGET OF EVALUATION OVERVIEW                      |          |

| 2 | TAR  | RGET OF EVALUATION DESCRIPTION                     | 22       |

|   | 2.1  | TOE DEFINITION                                     | 22       |

|   | 2.2  | SCOPE OF THE TOE                                   | 29       |

|   | 2.2. | 2.1 HARDWARE OF THE TOE                            |          |

|   | 2.2. | 2.2 FIRMWARE AND SOFTWARE OF THE TOE               |          |

|   | 2.2. | 2.3 INTERFACES OF THE TOE                          |          |

|   | 2.2. | 2.4 GUIDANCE DOCUMENTATION                         |          |

|   | 2.2. | 2.5 FORMS OF DELIVERY                              | 35       |

|   | 2.2. | 2.6 PRODUCTION SITES                               |          |

| 3 | cor  | NFORMANCE CLAIMS (ASE_CCL)                         | 37       |

|   | 3.1  | CC CONFORMANCE CLAIM                               |          |

|   | 3.2  | PP CLAIM                                           |          |

|   | 3.3  | PACKAGE CLAIM                                      | 38       |

|   | 3.4  | CONFORMANCE RATIONALE                              | 38       |

|   | 3.4. | 1.1 SECURITY PROBLEM DEFINITION                    | 38       |

|   | 3.4. | 1.2 CONFORMANCE RATIONALE                          | 38       |

|   | 3.4. | 1.3 ADDING OBJECTIVE                               |          |

|   | 3.4. | 1.4 AES AND TDES                                   |          |

|   | 3.4. | 1.5 LOADER                                         |          |

|   | 3.4. | 1.6 SHA                                            | 40       |

|   | 3.4. | 1.7 SUMMARY                                        | 40       |

|   | 3.5  | APPLICATION NOTES                                  | 41       |

| 4 | SEC  | CURITY PROBLEM DEFINITION (ASE_SPD)                | 42       |

|   | 4.1  | THREATS                                            | 42       |

|   | 4.1. | 1.1 ADDITIONAL THREAT DUE TO TOE SPECIFIC FUNCTION | NALITY42 |

|   | 4.1. | 2 ASSETS REGARDING THE THREATS                     | 43       |

|   | 4.2  | ORGANIZATIONAL SECURITY POLICIES                   | 44       |

|   | 4.2. | 2.1 AUGMENTED ORGANIZATIONAL SECURITY POLICY       | 44       |

|   | 4.3  | ASSUMPTIONS                                        | 46       |

|    | 4.3.      | 1   | AUGMENTED ASSUMPTIONS                                                  | 47                  |

|----|-----------|-----|------------------------------------------------------------------------|---------------------|

| 5  | SEC       | UR  | TY OBJECTIVES (ASE_OBJ)                                                | 48                  |

|    | 5.1       | S   | CURITY OBJECTIVES FOR THE TOE                                          | 48                  |

|    | 5.2       | S   | CURITY OBJECTIVES FOR THE DEVELOPMENT AND OPERATIONAL ENVIRONMENT      | 50                  |

|    | 5.2.      | 1   | CLARIFICATION OF "PROTECTION DURING COMPOSITE PRODUCT MANUFACTURING (C | DE.PROCESS-SEC-IC)" |

|    |           |     | 51                                                                     |                     |

|    | 5.3       | S   | CURITY OBJECTIVES RATIONALE                                            | 51                  |

| 6  | EXT       | EN  | DED COMPONENT DEFINITION (ASE_ECD)                                     | 54                  |

|    | 6.1       | С   | DMPONENT "SUBSET TOE SECURITY TESTING (FPT_TST)"                       | 54                  |

|    | 6.2       |     | EFINITION OF FPT_TST.2                                                 |                     |

|    | 6.3       | T   | SF SELF-TEST (FPT_TST)                                                 | 55                  |

| 7  | SEC       | UR  | TY REQUIREMENTS (ASE REQ)                                              | 56                  |

| •  |           |     |                                                                        |                     |

|    | 7.1       |     | DE SECURITY FUNCTIONAL REQUIREMENTS                                    |                     |

|    | 7.1.      | _   | EXTENDED COMPONENTS FCS_RNG.1 AND FAU_SAS.1                            |                     |

|    | 7.1       | 2   | SUBSET OF TOE TESTING                                                  |                     |

|    | 7.1.      | 3   | MEMORY ACCESS CONTROL                                                  |                     |

|    | 7.1.      | 4   | SUPPORT OF CIPHER SCHEMES                                              |                     |

|    | 7.1.      |     | DATA INTEGRITY                                                         |                     |

|    | 7.2       |     | JPPORT OF THE FLASH LOADER                                             |                     |

|    | 7.3       | Т   | DE SECURITY ASSURANCE REQUIREMENTS                                     |                     |

|    | 7.3.      | 1   | REFINEMENTS                                                            | 80                  |

|    | 7.4       | S   | CURITY REQUIREMENTS RATIONALE                                          | 84                  |

|    | 7.4.      | 1   | RATIONALE FOR THE SECURITY FUNCTIONAL REQUIREMENTS                     | 84                  |

|    | 7.4       | 2   | RATIONALE OF THE ASSURANCE REQUIREMENTS                                | 91                  |

| 8  | TOE       | SL  | MMARY SPECIFICATION (ASE_TSS)                                          | 93                  |

|    | 8.1       | S   | DPM: DEVICE PHASE MANAGEMENT                                           | 93                  |

|    | 8.2       | S   | PS: PROTECTION AGAINST SNOOPING                                        | 94                  |

|    | 8.3       | S   | PMA: PROTECTION AGAINST MODIFYING ATTACKS                              | 96                  |

|    | 8.4       | S   | PLA: PROTECTION AGAINST LOGICAL ATTACKS                                | 98                  |

|    | 8.5       | S   | CS: CRYPTOGRAPHIC SUPPORT                                              | 99                  |

|    | 8.5.      | 1   | TRIPLE DES                                                             | 99                  |

|    | 8.5       | 2   | AES                                                                    | 100                 |

|    | 8.5       | 3   | RSA                                                                    | 101                 |

|    | 8.5.      | 4   | ELLIPTIC CURVES EC                                                     | 104                 |

| Se | ecurity T | Γar | get Lite 6                                                             | 2015-10-30          |

## **Public** 8.5.5 8.5.6 8.5.7 8.5.8 8.6 ASSIGNMENT OF SECURITY FUNCTIONAL REQUIREMENTS TO TOE'S SECURITY FUNCTIONALITY .......107 8.7 11 GLOSSARY .......119

## **LIST OF TABLES**

| REVISION HISTORY                                                            | 4   |

|-----------------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                           | 5   |

| TABLE 1: IDENTIFICATION                                                     | 10  |

| TABLE 2: OPTIONS TO IMPLEMENT USER SOFTWARE AT INFINEON PRODUCTION PREMISES | 13  |

| TABLE 3: CONFIGURATION RANGES AND BLOCKING OPTIONS FOR THE USER             | 15  |

| TABLE 4 AUGMENTATIONS OF THE ASSURANCE LEVEL OF THE TOE                     | 37  |

| TABLE 5: THREATS ACCORDING PP [11]                                          | 42  |

| TABLE 7: ORGANIZATIONAL SECURITY POLICIES ACCORDING PP [11]                 | 44  |

| TABLE 9: OBJECTIVES FOR THE TOE ACCORDING TO PP [11]                        | 48  |

| TABLE 13: SECURITY FUNCTIONAL REQUIREMENTS DEFINED IN PP [11]               | 56  |

| TABLE 15: CRYPTOGRAPHIC TOE FUNCTIONALITY                                   | 65  |

| TABLE 20: REFERENCES OF HASH VALUES OF THE OPTIONAL CRYPTOGRAPHIC LIBRARIES | 114 |

## 1 Security Target Introduction (ASE\_INT)

## 1.1 Security Target and Target of Evaluation Reference

The title of this document is Security Target Lite, including optional Software Libraries RSA - EC - SHA-2 - Toolbox, for Common Criteria EAL6 augmented (EAL6+).

This document comprises the Infineon Technologies AG Security Controller (Integrated Circuit IC) M5073 G11 with specific IC dedicated firmware and optional software:

- RSA v2.03.008

- EC v2.03.008

- SHA-2 v1.01 and

- Toolbox v2.03.008

The target of evaluation (TOE) M5073 G11 is described in the following.

The reference to the belonging confidential Security Target is given chapter 9.

The Target of Evaluation (TOE) is the Infineon Security Controller M5073 G11 with optional RSA2048/4096 v2.03.008, EC v2.03.008, SHA-2 v1.01 and Toolbox v2.03.008 libraries and with specific IC dedicated software (firmware).

The design step of this TOE is G11.

The Security Target is based on the PP number 0084 "Security IC Platform Protection Profile with Augmentation Packages" [11] as publicly available for download at https://www.bsi.bund.de and certified under BSI-CC-PP-0084-2014.

The Protection Profile and the Security Target are built in compliance with Common Criteria v3.1. The Protection Profile is abbreviated with "PP" in the further.

The Security Target takes into account all relevant current final interpretations.

This TOE concept is based on the architecture, family concept and principles of the Integrity Guard implemented in the controllers by Infineon Technologies AG deemed for high security requiring applications.

The certification body of this process is the German BSI, whereas the abbreviation stands for Federal Office for Information Security, in German language Bundesamt für Sicherheit in der Informationstechnik.

Security Target Lite 9 2015-10-30

Table 1: Identification

| Object                               | Version           | Date       | Registration                                                                                                                                                                                                                                                                                       |  |  |

|--------------------------------------|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Security Target Lite (This document) | 0.6               | 2015-10-30 | M5073 G11                                                                                                                                                                                                                                                                                          |  |  |

| Target of Evaluation                 |                   |            | M5073 G11  With FW-Identifier 78.023.01.2  And following optional alternative SW - libraries: RSA2048 v2.03.008 RSA4096 v2.03.008 EC v2.03.008 and belonging User Guidance documentation.  And further optional software: SHA-2 v1.01 Toolbox v2.03.008 and belonging User Guidance documentation. |  |  |

| Protection Profile (PP)              | 1.0               | 2014-01-13 | Security IC Platform Protection Profile with Augmentation Packages BSI-CC-PP-0084-2014                                                                                                                                                                                                             |  |  |

| Common Criteria                      | 3.1<br>Revision 4 | 2012-09    | Common Criteria for Information Technology Security Evaluation  Part 1: Introduction and general model  CCMB-2012-09-001  Part 2: Security functional requirements  CCMB-2012-09-002  Part 3: Security Assurance Components CCMB-2012-09-003                                                       |  |  |

Chapter 2.2.4 describes briefly the contents of the individual documents of the User Guidance Documentation, while the individual documents are versioned and entitled in chapter 9 literature and references. The there listed set of user guidance documents belongs to the TOE.

The TOE can be identified with the Generic Chip Identification Mode (GCIM). The M5073 G11 hardware is identified by the bytes 05 and 06, which are the first two bytes of the chip identification number. The unique hexadecimal values for this TOE are: 00h 17h. This together with the other output data of design step, production side and firmware identifier clearly describes this unique TOE. More information is given in the hardware reference manual [1].

This TOE is represented by various products, differentiated by various configuration possibilities, done either by Infineon settings during production or, after delivery, by means of blocking at customer premises.

Despite these configuration possibilities, all products are derived from the equal hardware design results, the M5073 G11. All product derivatives are identically from module design, layout and footprint, but are made different in their possibilities to connect to different types of antennas or to a contact based interface only. Therefore, the TOE is represented and made out of different mask sets:

The main difference between the mask sets of the TOE is on one metal mask to implement different input capacitances in the analogue part of the radio frequency interface (RFI). This differentiation in the input capacitances allows the connection to a wider range of various antenna types, or respectively, to a contact based interface only. Note that external antennas or interfaces are not part of the TOE.

To each of the capacitances related mask sets belonging to the TOE, an individual value is assigned, which is part of the data output of the Generic Chip Identification Mode (GCIM). This number is located in the GCIM part individual length byte to clearly differentiate between the mask sets related to the different input capacitances. Thereby, the clear identification of the silicon design step is given.

There are no other differences between the mask sets the TOE is produced with. Details are explained in the user guidance hardware reference manual HRM [1]. An overview upon the different mask sets is given in the confidential Security Target [9].

The M5073 G11 allows for a maximum of configuration possibilities defined by the customer order or his blocking following the market needs For example, a M5073 G11 product can come in one project with the fully available SOLID FLASH™ NVM1 or in another project with any other SOLID FLASH™ NVM -size below the physical implementation size, or with a different RAM and user ROM size. And more, the user has the free choice, whether he needs the symmetric co-

<sup>&</sup>lt;sup>1</sup> Infineon® SOLID FLASH™ is an Infineon Trade Mark and stands for the Infineon EEPROM working as Flash memory. The abbreviation NVM is short for Non Volatile Memory.

processor SCP, or the asymmetric co-processor Crypto2304T, or both, or none of them. In addition, the user decides, whether the TOE comes with a free combination of software libraries or without any. And, to be even more flexible, various interface options can be chosen as well. To sum up the major selections, the user defines by his order:

- The available memory sizes of the SOLID FLASH™ NVM and RAM.

- The availability of the cryptographic coprocessors.

- The availability of the optional cryptographic libraries.

- The availability of the Flash Loader for available interfaces like ISO-7816, contactless ISO-14443.

- The availability of various interface options.

- The possibility to tailor the product by blocking on his own premises.

- The degree of freedom of the chip configuration is predefined by Infineon Technologies AG and made available via the order tool.

Beside fix TOE configurations, which can be ordered as usual, this TOE implements optionally the so called Bill-Per-Use (BPU) ability. This solution enables our customer to tailor the product on his own to the required configuration – project by project. By that BPU allows for significant reduction of logistic cost at all participating parties and serves for acceleration of delivery of tailored product to the end-user.

BPU enables our customers to block the chip on demand into the final configuration at his own premises, without further delivery or involving support by Infineon Technology. Further information is given in the confidential Security Target [9].

The entire configuration storage area is protected against manipulation, perturbation and false access. Note that the IFX-only part of the configuration page is already access protected prior delivery to the user and the TOE leaves the Infineon Technology premises only locked into User Mode.

The Flash Loader BPU software part is only available on the products which have been ordered with the BPU option. In all other cases this software is disabled on the product. If a product is ordered without Flash Loader, also the Flash Loader BPU software part is disabled and the BPU configuration changes are blocked in the IFX-configuration, which additionally renders the BPU functionality unusable. Various delivery combinations are given and for example, a product can come with a fix configuration and with Flash Loader, to enable the user to download software, but without BPU option. Following cases can occur:

- Order in fixed configuration, without Flash Loader feature:

no download of user software and no blocking possibility after delivery

- Order in fixed configuration with Flash Loader but without BPU option:

download of user software but no blocking possibility after delivery

Security Target Lite 12 2015-10-30

Order with Flash Loader feature and Bill-per-Use option in starting configuration:

final chip configuration by the user and download of user software

Beside the various TOE configurations further possibilities of how the user inputs his software on the TOE, i.e. the operating system and applications, are in place. This provides a maximum of flexibility and for this an overview is given in the following table:

Table 2: Options to implement user software at Infineon production premises

| 1. | The user or/and a subcontractor downloads the software into the SOLID FLASH™ NVM on his own.  Infineon Technologies AG has not received user software and there are no user data in the ROM.                          | The Flash Loader can be activated by the user or subcontractor to download his software in the SOLID FLASH™ NVM — until the Flash Loader is finally deactivated by the user.                                                                                                                         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | The user provides software for the download into the SOLID FLASH™ NVM to Infineon Technologies AG. The software is downloaded to the SOLID FLASH™ NVM during chip production. I.e. there are no user data in the ROM. | The Flash Loader is disabled.                                                                                                                                                                                                                                                                        |

| 3  | The user provides software for the download into the SOLID FLASH™ NVM to Infineon Technologies AG. The software is downloaded to the SOLID FLASH™ NVM during chip production. I.e. there are no user data in the ROM  | The Flash Loader is blocked afterwards but can be activated or reactivated by the user or subcontractor to download his software in the SOLID FLASH™ NVM. Precondition is that the user has provided an own reactivation procedure in software prior chip production to Infineon Technologies AG.    |

| 4  | The user provides the software for implementation into the ROM mask.                                                                                                                                                  | The Flash Loader is disabled.                                                                                                                                                                                                                                                                        |

| 5  | The user provides the software for implementation into the ROM mask.                                                                                                                                                  | The FL is blocked afterwards but can be activated or reactivated by the user or subcontractor to download his software in the Infineon® SOLID FLASH™ memory. Precondition is that the user has provided an own reactivation procedure in software prior chip production to Infineon Technologies AG. |

Security Target Lite 13 2015-10-30

| 6 | The user provides the software for implementation into the ROM mask and provides software for the download into the SOLID FLASH™ NVM to Infineon Technologies AG. | The Flash Loader is disabled.                                                                                                                                                                                                                                                                                  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 | The user provides the software for implementation into the ROM mask and provides software for the download into the SOLID FLASH™ NVM to Infineon Technologies AG. | The Flash Loader is blocked afterwards but can be activated or reactivated by the user or subcontractor to download his software in the Infineon® SOLID FLASH™ memory. Precondition is that the user has provided an own reactivation procedure in software prior chip production to Infineon Technologies AG. |

For the cases with active Flash Loader and whenever the user has finalized his SW-download, respectively the TOE is in the final state and about to be delivered to the end-user, the user is obligated to lock the Flash Loader. The locking is the final step and results in a permanent disabling of the Flash Loader. This means that once being in the locked status, the Flash Loader cannot be reactivated anymore.

Note that wherever a TOE comes with disabled Flash Loader, the BPU feature is not possible as well. On the other hand, an ordered active Flash Loader can come without the BPU feature. The availability of the BPU feature depends on the user order but is only given on products with active Flash Loader.

The following listing contains the memory size ranges and other blocking options, focusing on the maximum respectively minimum user available limitations. Within those limitations the TOE configurations can vary under only one identical IC-hardware, regardless whether the configurations are set by Infineon or within further limitations by the user. All configurations the TOE is made off and all thereof resulting derivatives have no impact on security and are covered by the certificate.

Wherever user blocking is stated in the table below, the user can block the chip within the therein defined limitations, but only if the product was ordered with the BPU option.

The below given configuration possibilities are valid unchanged throughout the mentioned different mask sets. Wherever user blocking is stated below, the user can block the chip within the defined limitations, but only if the product was ordered with the user configuration capability.

The following table provides an excerpt of possible configurations:

Table 3: Configuration ranges and blocking options for the user

| Module / Feature (User view)            | Max-Value<br>(User view) | Min-Value (User view) | User Blocking | User Blocking<br>Step |

|-----------------------------------------|--------------------------|-----------------------|---------------|-----------------------|

| Memories                                |                          |                       |               |                       |

| SOLID FLASH™ NVM                        | 628 kBytes               | 0 kBytes              | Yes           | 1 kBytes              |

| ROM                                     | 444 kBytes               | 0 kBytes              | By order only | n.a.                  |

| RAM for the user                        | 12 kBytes                | 1 kBytes              | Yes           | 1kBytes               |

| Modules                                 |                          |                       |               |                       |

| Crypto2304T                             | Available                | Not available         | Yes           | On/off                |

| SCP                                     | Available                | Not available         | Yes           | On/off                |

| Interfaces                              |                          |                       |               |                       |

| ISO 7816-3 slave                        | Available                | Not available         | Yes           | On/off                |

| Inter Integrated Circuit I2C            | Available                | Not available         | Yes           | On/off                |

| RFI – ISO 14443<br>generally            | Available                | Not available         | Yes           | On/off                |

| ISO 14443 Type A card mode              | Available                | Not available         | By order only | None                  |

| ISO 14443 Type B card mode              | Available                | Not available         | By order only | None                  |

| ISO 18092 NFC passive mode              | Available                | Not available         | By order only | None                  |

| Software controlled Input Output (SWIO) | Available                | Available             | No            | No                    |

| Mifare hardware support for card mode   | Available                | Not available         | By order only | None                  |

There are further communication modes and blocking options available which are outlined in the confidential Security Target [9] and in the confidential User Guidance.

All possible TOE configurations equal and/or within the physical specified ranges as outlined in the confidential Security Target [9] and the hardware reference manual HRM [1] are covered by the certificate.

Beside the above listed flexible ranges, the user guidance contains a number of predefined configurations for those customers not making use of the BPU option. All of these configurations belong to the TOE as well and are of course made of the equal hardware and are inside the above declared ranges.

Today's predefined configurations of the TOE are listed in the hardware reference HRM [1]. These predefined products come with the most requested configurations and allow to produce volumes on stock in order to simplify logistic processes.

According to the BPU option, a non-limited number of configurations of the TOE may occur in the field. The number of various configurations depends on the user and purchase contract only.

Note that the TOE outputs Generic Chip Identification data enabling the user together with the user guidance for a clear interpretation and identification of the TOE. More information is given in the confidential Security Target [9].

All these steps for gathering identification and detailed configuration information can be done by the user himself, without involving Infineon Technologies AG.

The TOE consists of the hardware part, the firmware parts and the optional software parts. The Smartcard Embedded Software, i.e. the operating system and applications are not part of the TOE.

The firmware parts are the RMS library, the Service Algorithm Minimal (SA), the STS firmware for test purpose (see chapter 2.2.2), providing some functionality via an API to the Smartcard Embedded Software, the Flash Loader for downloading user software to the SOLID FLASH™ NVM and the Mifare compatible software interface. The entire firmware is located in the ROM and the belonging patches are stored in the SOLID FLASH™ NVM.

The software parts are differentiated into the cryptographic libraries RSA<sup>1</sup>, EC<sup>2</sup> and SHA-2<sup>3</sup> and the supporting libraries Toolbox and Base. RSA, EC, SHA-2 and Toolbox provide certain functionality via an API to the Smartcard Embedded Software. The Base Library is only used internally by the RSA, EC and Toolbox libraries and has no user interface. If none the three libraries RSA, EC and Toolbox is delivered, also the Base Library is not on board. The SHA-2 library does not use the Base Library.

Security Target Lite 16 2015-10-30

$<sup>^{1}\, {\</sup>hbox{\rm Rivest-Shamir-Adleman asymmetric cryptographic algorithm}}$

<sup>&</sup>lt;sup>2</sup> The Elliptic Curve Cryptography is abbreviated with EC only in the further, in order to avoid conflicts with the abbreviation for the Error Correction Code ECC.

<sup>&</sup>lt;sup>3</sup> SHA Secure Hash Algorithm

The TOE can be delivered including - in free combinations - or not including any of the functionality of the cryptographic libraries EC, RSA, SHA-2 and the supporting Toolbox library. If RSA or EC or Toolbox is delivered, automatically the Base Library is part of the shipment too. It is regardless which version of the cryptographic libraries the user may choose.

If the user decides not to use one or all of the crypto library(s), the specific library(s) is (are) not delivered to the user and the accompanying "Additional Specific Security Functionality (O.Add-Functions)" *Rivest-Shamir-Adleman (RSA)* and/ or Elliptic Curve Cryptography (*EC*) is/are not provided by the TOE.

The Toolbox library provides the user optionally basic arithmetic and modular arithmetic operations, in order to support user software development using long integer operations. These basic arithmetic operations do not provide any security functionality, implement no security mechanism, and do not proved additional specific security functionality - as defined for the cryptographic libraries.

The user developed software using the Toolbox basic operations is not part of the TOE.

The Base Library provides the low level interface to the asymmetric cryptographic coprocessor and has no user available interface. The Base Library does not provide any security functionality, implements no security mechanism, and does not provide additional specific security functionality.

Deselecting one of the libraries does not include the code implementing functionality, which the user decided not to use. Not including the code of the deselected functionality has no impact of any other security policy of the TOE; it is exactly equivalent to the situation where the user decides just not to use the functionality.

The RSA, EC, SHA-2 and Toolbox libraries can be loaded, together with the Smartcard Embedded software, into the SOLID FLASH™ NVM. This holds also for the Base Library, if the RSA, EC or Toolbox or combinations hereof is/are part of the shipment.

All other Smartcard Embedded Software does not belong to the TOE and is not subject of the evaluation.

## 1.2 Target of Evaluation overview

The TOE comprises the Infineon Technologies Dual Interface Security Controller M5073 G11 with specific IC dedicated software and optional RSA, EC, SHA-2 and Toolbox libraries.

The TOE is a member of the Infineon Technologies AG high security controller family meeting the highest requirements in terms of performance and security. A summary product description is given in this Security Target (ST).

This TOE is intended to be used in any application and device requiring the highest level of security, and can be used for example not only as a secure smart card, but also as a secure element on a printed circuit board or similar. The capabilities of this TOE can be used almost everywhere, where highly secure applications are in use and of course in any other application as well. This TOE is deemed for governmental, corporate, transport and payment markets, or wherever a secure root of trust is required. Various types of applications can use this TOE in almost any device or form factor, for example in closed loop logical access controls, physical access controls, secure internet access control and internet authentication, or as multi-application token or simply as encrypted storage.

Security Target Lite 17 2015-10-30

This member of the high security controller family features a security philosophy focusing on data integrity instead of numerous sensors. By that two main principles combined in close synergy are utilized in the security concept called the "Integrity Guard". These main principles are the comprehensive error detection, including the dual CPU, and the full encrypted data path, leaving no plain data on the chip. These principles proved that they provide excellent protection against invasive and non-invasive attacks known today.

The intelligent shielding algorithm finishes the layers, finally providing the so called intelligent implicit active shielding "l²-shield". This provides physical protection against probing and forcing.

This dual interface controller is able to communicate using either the contact based or the contactless interface. The implemented dual interface provides a maximum flexibility in using following communication protocols respectively methods:

#### Contact based interfaces

ISO 7816,

This is the ISO defined standard contact based communication protocol, using the pads.

Inter Integrated Circuit (I2C)

The Inter-Integrated Circuit (I2C, also IIC) module is able to be connected as slave to an external multi-master-serial-bus-system used to connect the TOE to an external master. The IIC protocol software is not part of the TOE.

There is a further communication mode which is outlined in the confidential Security Target [9].

#### **Contactless interfaces**

ISO 14443 Type A and Type B

These are ISO defined proximity contactless protocols using an external antenna and the TOE implemented analogue and digital radio frequency interface.

ISO/IEC 18092 passive mode,

This is an ISO defined proximity contactless protocol using an external antenna and the TOE implemented analogue and digital radio frequency interface.

Mifare compatible Interface,

This is a proprietary proximity contactless protocol using an external antenna and the TOE implemented analogue and digital radio frequency interface, as well as the memory part reserved for Mifare use.

And various further communication modes.

All interfaces and protocols can be made available sequentially. How the interfaces are used or combined depends exclusively on the user software.

Further communication modes, details and an overview about their combinations are outlined in the confidential Security Target [9].

Security Target Lite 18 2015-10-30

The TOE provides a real 16-bit CPU-architecture and is compatible to the MCS®251 instruction set with an execution time faster than a standard MCS®251 microcontroller at the same clock frequency. The major components of the core system are the dual CPU (Central Processing Units), acting as one, the MMU (Memory Management Unit) and MED (Memory Encryption/Decryption Unit). The dual CPU controls each other in order to detect faults and serve by this for data integrity. The TOE implements a full 16 MByte linear addressable memory space for each privilege level, a simple scalable Memory Management concept and a scalable stack size. The flexible memory concept consists of ROM- and Flashmemory as part of the nonvolatile memory (NVM), respectively SOLID FLASH™ NVM. For the SOLID FLASH™ NVM the Unified Channel Programming (UCP) memory technology is used.

The RMS library providing some functionality via an API to the Smartcard Embedded Software contains for example SOLID FLASH™ NVM service routines. The Service Algorithm provides functionality for the tearing save write into the SOLID FLASH™ NVM. The STS firmware is used for test purposes during start-up and the Flash Loader allows downloading user software to the SOLID FLASH™ NVM during the manufacturing process. The firmware parts are implemented in the ROM and in access protected areas of the SOLID FLASH™ NVM.

The BSI has changed names and abbreviations for Random Number Generators, which is clarified as follows: The Physical True Random Number Generator (PTRG), also named True Random Number Generator (TRNG) is a physical random number generator and meets the requirements of the functionality class AIS31 PTG.2, see [15]. It is used for provision of random number generation as a security service to the user and for internal purposes. The produced genuine random numbers can be used directly or as seed for the Deterministic Random Number Generator (DRNG), former named as Pseudo Random Number Generator (PRNG). The DRNG respectively PRNG is not in the scope of the evaluation. The TRNG respectively PTRNG is specially designed for smart cards, but can also be used in any other application where excellent physical random data are required.

The two cryptographic co-processors serve the need of modern cryptography: The symmetric co-processor (SCP) combines both AES and Triple-DES with dual-key or triple-key hardware acceleration. The Asymmetric Crypto Co-processor, called Crypto2304T performs RSA-2048 bit (4096-bit with CRT) and Elliptic Curve (EC) cryptography.

The software part of the TOE consists of the cryptographic RSA-, EC- and the SHA-2 libraries and the supporting Toolbox and Base Libraries. If RSA or EC or Toolbox or combinations hereof are part of the shipment, automatically the Base Library is included.

The RSA library is used to provide a high level interface to RSA (Rivest, Shamir, Adleman) cryptography implemented on the hardware component Crypto2304T and includes countermeasures against SPA, DPA and DFA attacks. The routines are used for the generation of RSA Key Pairs (RsaKeyGen), the RSA signature verification (RsaVerify), the RSA signature generation (RsaSign) and the RSA modulus recalculation (RsaModulus). The hardware Crypto2304T unit provides the basic long number calculations (add, subtract, multiply, square with 1100 bit numbers) with high performance. The RSA library is delivered as object code and in this way integrated in the user software. The RSA library can perform RSA operations

Security Target Lite 19 2015-10-30

from 512 to 4096 bits.

Following the BSI<sup>1</sup> recommendations, key lengths below 1976 bit are not included in the certificate.

The EC library is used to provide a high level interface to Elliptic Curve cryptography implemented on the hardware component Crypto2304T and includes countermeasures against SPA, DPA and DFA attacks. The routines are used for ECDSA signature generation, ECDSA signature verification, ECDSA key generation and Elliptic Curve Diffie-Hellman key agreement. In addition, the EC library provides an additional function for calculating primitive elliptic curve operations like ECC Add and ECC Double. EC curves over prime field Fp, as well as over GF(2<sup>n</sup>) finite field are supported too. Note that the according user guidance the Elliptic Curve cryptographic functions are abbreviated using ECC.

The EC library is delivered as object code and in this way integrated in the user software. The certification covers the standard NIST [17] and Brainpool [18] Elliptic Curves with key lengths of 160, 163, 192, 224, 233, 256, 283, 320, 384, 409, 512 or 521 Bits, due to national AIS32 regulations by the BSI. Numerous other curve types, being also secure in terms of side channel attacks on this TOE, exist, which the user optionally can add in the composition certification process.

The SHA-library provides the calculation of a hash value of freely chosen data input in the CPU. The SHA-library is delivered as object code and is in this way available for the user software. This secure hash-algorithm SHA-2 is intended to be used for hashing any type of user data. Further essential information about the usage is given in the confidential user guidance.

The Toolbox library does not provide cryptographic support or additional security functionality as it provides only the following basic long integer arithmetic and modular functions in software, supported by the cryptographic coprocessor: Addition, subtraction, division, multiplication, comparison, reduction, modular addition, modular subtraction, modular multiplication, modular inversion and modular exponentiation. No security relevant policy, mechanism or function is supported. The Toolbox library is deemed for software developers as support for simplified implementation of long integer and modular arithmetic operations.

The Base Library provides the low level interface to the asymmetric cryptographic coprocessor and has no user available interface. The Base Library does not provide any security functionality, implements no security mechanism, and does not provide additional specific security functionality.

Note that this TOE can come with both cryptographic co-processors accessible, or with a blocked SCP or with a blocked Crypto2304T, or with both cryptographic co-processors blocked. The blocking depends on the user's choice. No accessibility of the deselected cryptographic co-processors is without impact on any other security policy of the TOE; it is exactly equivalent to the situation where the user decides just not to use the cryptographic co-processors. The TOE can also be delivered without a specific optional software library. In this case the TOE does not provide the Additional Specific Security Functionality Rivest-Shamir-Adleman Cryptography (RSA) or/and Elliptic Curve Cryptography (EC) or/and SHA-2.

\_

$<sup>^{</sup>f 1}$  BSI Bundesamt für Sicherheit in der Informationstechnik – Federal Office for Information Security

To fulfill the highest security standards for smartcards today and also in the future, this TOE implements a progressive digital security concept, which already has been certified in various forerunner processes and which has proven its resistance against attackers with high attack potential. This TOE utilizes digital security features to include customer friendly security, combined with a robust design overcoming the disadvantages on analogue protection technologies. The TOE provides full on-chip encryption of the data path, covering the core including the ALUs of the CPUs, busses, memories and cryptographic co-processors leaving no plaintext on the chip. Therefore the attractiveness for attackers is extremely reduced as encrypted signals are of no use for the attacker – neither for manipulation nor for eavesdropping.

In addition, the TOE is equipped with a comprehensive error detection capability for the complete data path. The dual CPU approach allows error detection even while processing. A comparator detects whether a calculation was performed without errors. This approach does not leave any parts of the core circuitry unprotected. The concept allows that the relevant attack scenarios are detected, whereas other conditions that would not lead to an error would mainly be ignored. That renders the TOE robust against environmental influences.

Subsequently, the TOE implements what we call intelligent implicit shielding (I<sup>2</sup>). These measures constitute a shield on sensitive and security relevant signals which is not recognizable as a shield. This provides excellent protection against invasive physical attacks, such as probing, forcing or similar.

In this security target the TOE is described and a summary specification is given. The security environment of the TOE during its different phases of the lifecycle is defined. The assets are identified which have to be protected through the security policy. The threats against these assets are described. The security objectives and the security policy are defined, as well as the security requirements. These security requirements are built up of the security functional requirements as part of the security policy and the security assurance requirements. These are the steps during the evaluation and certification showing that the TOE meets the targeted requirements. In addition, the functionality of the TOE matching the requirements is described.

The assets, threats, security objectives and the security functional requirements are defined in this Security Target and in the PP [11] and are referenced here. These requirements build up a minimal standard common for all Smartcards.

The security functions are defined here in the security target as property of this specific TOE. Here it is shown how this specific TOE fulfills the requirements for the common standard defined in the Common Criteria documents [12], [13], [14] and in the PP [11].

Security Target Lite 21 2015-10-30

## 2 Target of Evaluation Description

The TOE description helps to understand the specific security environment and the security policy. In this context the assets, threats, security objectives and security functional requirements can be employed. The following is a more detailed description of the TOE than in the Security IC Platform Protection Profile PP [11] as it belongs to the specific TOE.

The Security IC Platform Protection Profile is in general often abbreviated with 'PP' and its version number.

## 2.1 TOE Definition

This TOE consists of a Security Dual Interface Controllers as integrated circuits (IC), meeting the highest requirements in terms of performance and security. The TOE products are manufactured by Infineon Technologies AG in a 90 nm CMOStechnology (L90).

This TOE is intended to be used in smart cards and any other form factor for particularly applications requiring highest levels of security and for its previous use as developing platform for smart card operating systems according to the lifecycle model from Protection Profile the PP [11].

The term Smartcard Embedded Software is used in the following for all operating systems and applications stored and executed on the TOE. The TOE is the platform for the Smartcard Embedded Software. The Smartcard Embedded Software itself is not part of the TOE.

The TOE consists of a core system, memories, co-processors, peripherals, security modules and analogue peripherals.

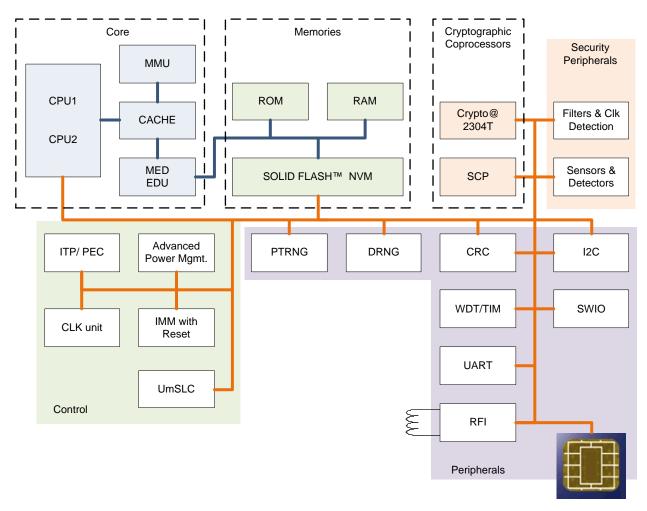

Following diagram provides a simplified overview upon the hardware subsystems which are briefly described below:

Security Target Lite 22 2015-10-30

Figure 1: Simplified block diagram of the TOE

The main components of the core system are the dual CPU (Central Processing Units) including the internal encryption leaving no plain data anywhere, the MMU (Memory Management Unit), the MED (Memory Encryption/Decryption Unit) and the CACHE memory.

The CPU – here the two processor parts (CPU1 and CPU2) are seen from functional perspective as one - is compatible with the instruction set of the forerunner family 66-PE and is therefore also compatible to the SAB 80251 instruction set (8051 is a subset hereof) and to the MCS® 251 instruction set which is enhanced. Anyhow, the dual-CPU is faster than the standard processor at the equal clock frequency. It provides additional powerful instructions for smart card or other applications. It thus meets the requirements for the new generation of operating systems. Despite its compatibility the CPU implementation is entirely proprietary and not standard.

The two processor parts of the CPU control each other in order to detect faults and maintain by this the data integrity. A comparator detects whether a calculation was performed without errors and allows error detection even while processing. Therefore the TOE is equipped with a comprehensive error detection capability, which is designed to leave no relevant parts of the circuitry unprotected.

The CPU accesses the memory via the integrated Memory Encryption and Decryption unit (MED), which transfer the data from the memory encryption schema to the CPU encryption schema without decrypting into intermediate plain data. The error detection unit (EDU) automatically manages the error detection of the individual memories and detects incorrect transfer of data between the memories by means of error code comparison.

The access rights of the firmware, user operating system and application to the memories are controlled and enforced by the memory management unit (MMU).

The CACHE memory – or simply, the CACHE – is a high-speed memory-buffer located between the CPU and the (external) main memories holding a copy of some of the memory contents to enable access to the copy, which is considerably faster than retrieving the information from the main memory. In addition to its fast access speed, the CACHE also consumes less power than the main memories. All CACHE systems own their usefulness to the principle of locality, meaning that programs are inclined to utilize a particular section of the address space for their processing over a short period of time. By including most or all of such a specific area in the CACHE, system performance can be dramatically enhanced. The implemented post failure detection identifies and manages errors if appeared during storage.

The controllers of this TOE store both code and data in a linear 16-MByte memory space, allowing direct access without the need to swap memory segments in and out of memory using a memory management unit.

The memory block contains the ROM, RAM and the SOLID FLASH™ NVM. All data of the memory block is encrypted and all memory types are equipped with an error detection code (EDC), the SOLID FLASH™ NVM in addition with an error correction code (ECC). Errors in the memories are automatically detected (EDC) and in terms of the SOLID FLASH™ NVM 1-Bit-errors are also corrected (ECC). The TOE uses also Special Function Registers SFR. These SFR registers are used for general purposes and chip configuration. These registers are located in the SOLID FLASH™ NVM as configuration area page.

The non-volatile ROM contains the firmware parts and, if desired by the user, also user software. If this is the case, the user must provide his software package for the ROM prior production, as the software is processed as a hardware mask during chip production and implementation of the ROM. The firmware part STS of the ROM is accessible for Infineon only. The RAM is a volatile memory and used by the core.

The coprocessor block contains the two co-processors for cryptographic operations are implemented on the TOE: The Crypto2304T for calculation of asymmetric algorithms like RSA and Elliptic Curve (EC) and the Symmetric Cryptographic Processor (SCP) for dual-key or triple-key triple-DES and AES calculations. These co-processors are especially designed for smart card applications with respect to the security and power consumption, but can of course be used in any other application of form factor where suitable. The SCP module computes the complete DES algorithm within a few clock cycles and is especially designed to counter attacks like DPA, EMA and DFA.

Note that this TOE can come with both crypto co-processors accessible, or with a blocked SCP or with a blocked Crypto2304T, or with both crypto co-processors blocked. The blocking depends on the customer demands prior to the production of the hardware. No accessibility of the deselected cryptographic co-processors is without impact on any

Security Target Lite 24 2015-10-30

other security policy of the TOE; it is exactly equivalent to the situation where the user decides just not to use the cryptographic co-processors.

The security peripherals block contains the small remaining set of sensors and filters. This small set of sensors is left in order to detect excessive deviations from the specified operational range, while not being over-sensitive. These features do not need adjustment or calibration and makes the chip even more robust. Conditions that would not be harmful for the operation would in most cases not influence the proper function. The small set of sensors is not necessary for the chip security but serve for robustness. Having the integrity guard concept in place, the sensors - except a single one - are no more required for the TOE security. The only sensor left, contributing to a security mechanism, is the frequency sensor. All other sensors are assigned to be security supporting only.

The filters are on board to make the TOE more robust against perturbations on the supply lines.

The block control is constituted out of the modules Interrupt Controller (ITP) and Peripheral Event Channel controller (PEC), the modules Clock unit, the Advanced Power Management, the Interface Management Module with Reset and the UmSLC, which is the abbreviation for User Mode Security Life Control. The UmSLC enables for checking the proper functions of modules and subsystems and checks the correct operation of the TOE.

The implemented clock management is optimized to reduce the overall power consumption. Contactless products provide a low-power halt mode for operation with reduced power consumption. The Clock Unit (CLKU) supplies the clocks for all components of the TOE. The Clock Unit can work in an internal and external clock mode. The system frequency can be configured and this enables a programmer to choose the best-fitting frequency for an application in consideration of a potential current limit and a demanded application performance.

The peripherals block is constituted out of PTRNG, DRNG, CRC, Timer & WDT, the RFI, I2C, SWIO and the UART. The modules are briefly described in the following:

The TRNG respectively PTRNG is specially designed for smart cards, but can also be used in any other application where excellent physical random data are required. The TRNG respectively PTRNG fulfills the requirements from the functionality class PTG.2 of the AIS31 and produces genuine random numbers which then can be used directly or as seed for the Deterministic Random Number Generator (DRNG), former named as Pseudo Random Number Generator (PRNG). The DRNG respectively PRNG is not in the scope of the evaluation.

The cyclic redundancy check (CRC) module is a checksum generator. The checksum is a unique number associated with a message or another block of data consisting of several bytes. The idea of the CRC method is to treat the input data as a binary bit stream and divide that stream by a fixed binary number. The remainder of that division is the CRC checksum.

The timer enables for easy implementation of communication protocols such as T=1 and all other time-critical operations. The timer can be programmed for particular applications, such as measuring the timing behavior of an event. Timer events can generate interrupt requests to be used for peripheral event channel data transfers. The watchdog is implemented to provide the user some additional control of the program flow. More details are given in the hardware reference module HRM [1].

Security Target Lite 25 2015-10-30

This dual interface controller is able to communicate using either the contact based or the contactless interface. The implemented dual interface provides a maximum flexibility in using following communication protocols respectively methods:

#### Contact based interfaces

ISO 7816

This is the ISO defined standard contact based communication protocol, using the pads.

• Inter Integrated Circuit (I2C)

The Inter-Integrated Circuit (I2C, also IIC) module is able to be connected as slave to an external multi-master-serial-bus-system used to connect the TOE to an external master, using the IIC protocol. The master can also be a multi master IIC system. The IIC protocol software is not part of the TOE.

And further communication modes which are outlined in the confidential Security Target [9].

#### **Contactless interfaces**

ISO 14443 Type A and Type B

These are ISO defined proximity contactless protocols using an external antenna and the TOE implemented analogue and digital radio frequency interface.

ISO/IEC 18092 passive mode,

This is an ISO defined proximity contactless protocol using an external antenna and the TOE implemented analogue and digital radio frequency interface.

Mifare compatible Interface,

This is a proprietary proximity contactless protocol using an external antenna and the TOE implemented analogue and digital radio frequency interface, as well as the memory part reserved for Mifare use.

And various further communication modes.

All interfaces and protocols can be made available sequentially. How the interfaces are used or combined depends exclusively on the user software.

Further communication modes, details and an overview about their possible parallel usage are outlined in the confidential Security Target [9].

This flexibility enables for example also for bypassing the coding/decoding of the RFI and leaves its interpretation up to the software. By that further and also proprietary protocols can be implemented by the user software. Note that anything contacting from outside the chip and also any user software managing the communication are not part of this TOE.

The individual combinations of the interface options are depicted in the confidential Security Target [9].

Security Target Lite 26 2015-10-30

Supporting a Mifare compatible Interface application requires a dedicated small space of memory. In this context and depending on user's choice, various memory sections each of 1 up to 4 kBytes can be defined. The number and location of these memory sections is simply limited by the available SOLID FLASH™ NVM space. Also these memory sections are read/write protected and are defined and generated by the user.

The bus system comprises two separate bus entities: a memory bus supporting and a peripheral bus for high-speed communication with the peripherals.

Subsequently, an intelligent shielding algorithm finishes the layers, finally providing the so called intelligent implicit active shielding "l<sup>2</sup>-shield". This provides physical protection against probing and forcing.

The STS (self-test software), RMS (Resource Management System), Service Algorithm Minimal (SA) and Flash Loader together compose the TOE firmware stored in the ROM and the patches hereof in the SOLID FLASH™ NVM. All mandatory functions for internal testing, production usage and start-up behavior (STS), and also the RMS and SA functions are grouped together in a common privilege level. These privilege levels are protected by a hardwired Memory Management Unit (MMU) setting.

The user software can be implemented in various options depending on the user's choice as described in chapter 1.1. Thereby the user software, or parts of it, can be downloaded into the SOLID FLASH™ NVM, either during production of the TOE or at customer side. In the latter case, the user downloads his software or the final parts of it at his own premises, using the Flash Loader software.

The SHA-library provides the calculation of a hash value of freely chosen data input in the CPU. The SHA-library is delivered as object code and is in this way available for the user software.

This secure hash-algorithm SHA-2 is intended to be used for signature generation, verification and generic data integrity checks. This secure hash-algorithm SHA-2 is intended to be used for hashing any type of user data. Further essential information about the usage is given in the confidential user guidance.

The toolbox library does not provide cryptographic support or additional security functionality as it provides only the following basic long integer arithmetic and modular functions in software, supported by the cryptographic coprocessor: Addition, subtraction, division, multiplication, comparison, reduction, modular addition, modular subtraction, modular multiplication, modular inversion and modular exponentiation. No security relevant policy, mechanism or function is supported. The toolbox library is deemed for software developers as support for simplified implementation of long integer and modular arithmetic operations.

The Base Library provides the low level interface to the asymmetric cryptographic coprocessor and has no user available interface. The base library does not provide any security functionality, implements no security mechanism, and does not provide additional specific security functionality.

The RSA library is used to provide a high level interface to RSA (Rivest, Shamir, Adleman) cryptography implemented on the hardware component Crypto2304T and includes countermeasures against SPA, DPA and DFA attacks. The routines are used for the generation of RSA Key Pairs (RsaKeyGen), the RSA signature verification (RsaVerify), the RSA signature

Security Target Lite 27 2015-10-30

generation (RsaSign) and the RSA modulus recalculation (RsaModulus). The hardware Crypto2304T unit provides the basic long number calculations (add, subtract, multiply, square with 1100 bit numbers) with high performance. The RSA library is delivered as object code and in this way integrated in the user software. The RSA library can perform RSA operations from 512 to 4096 bits.

Following the BSI<sup>1</sup> recommendations, key lengths below 1976 bit are not included in the certificate.

The EC library is used to provide a high level interface to Elliptic Curve cryptography implemented on the hardware component Crypto2304T and includes countermeasures against SPA, DPA and DFA attacks. The routines are used for ECDSA signature generation, ECDSA signature verification, ECDSA key generation and Elliptic Curve Diffie-Hellman key agreement. In addition, the EC library provides an additional function for calculating primitive elliptic curve operations like ECC Add and ECC Double. EC curves over prime field Fp, as well as over GF(2<sup>n</sup>) finite field are supported too. Note that the according user guidance the Elliptic Curve cryptographic functions are abbreviated using ECC.

The EC library is delivered as object code and in this way integrated in the user software. The certification covers the standard NIST [17] and Brainpool [18] Elliptic Curves with key lengths of 160, 163, 192, 224, 233, 256, 283, 320, 384, 409, 512 or 521 Bits, due to national AIS32 regulations by the BSI. Numerous other curve types, being also secure in terms of side channel attacks on this TOE, exist, which the user optionally can add in the composition certification process.

Note that this TOE can come with both cryptographic co-processors accessible, or with a blocked SCP or with a blocked Crypto2304T, or with both cryptographic co-processors blocked. The blocking depends on the user's choice. No accessibility of the deselected cryptographic co-processors is without impact on any other security policy of the TOE; it is exactly equivalent to the situation where the user decides just not to use the cryptographic co-processors. The TOE can be delivered without a specific library. In this case the TOE does not provide the Additional Specific Security Functionality Rivest-Shamir-Adleman Cryptography (RSA) or/and Elliptic Curve Cryptography (EC) or/and SHA-2.

The TOE sets a new, improved standard of integrated security features, thereby meeting the requirements of all smart card and other related applications or form factors, such as information integrity, access control, mobile telephone and identification, as well as uses in electronic funds transfer and healthcare systems.

To sum up, the TOE is a powerful dual interface security controller with a large amount of memory and special peripheral devices with improved performance, optimized power consumption, free to choose contact based or contactless operation, at minimal chip size while implementing high security. It therefore constitutes the basis for future smart card and other related applications or form factors.

\_

Security Target Lite 28 2015-10-30

$<sup>^{</sup>f 1}$  BSI Bundesamt für Sicherheit in der Informationstechnik – Federal office for information security

## 2.2 Scope of the TOE

The TOE comprises several types of hardware each differing by slight mask set changes to allow for maximum flexibility in terms of connection to antennas and implementation into different package and module types. All these changes have no influence on the security or any security policy related to the TOE.

Therefore, this TOE includes:

- The silicon die, respectively the Integrated Circuit (IC) respectively the hardware of this TOE, in several versions.

The versions differ from each other by the interface capabilities: The IC is comes with a variety of interface capacitances, enabling connections to a variety of external antennas, or to be operated contact based only.

- The TOE is also delivered in various configurations, achieved by means of blocking by the customer and/or depending on the customer order.

- All configurations and resulting derivatives generated out of the mask sets described as above.

- · All according firmware and

- Optional software in various combinations as ordered.

- All configurations of any individual TOE product.

All product derivatives of this TOE, including all configuration possibilities differentiated by the GCIM data and the configuration information output, are manufactured by Infineon Technologies AG. In the following descriptions, the term "manufacturer" stands short for Infineon Technologies AG, the manufacturer of the TOE.

New configurations can occur at any time depending on the user blocking or by different configurations applied by the manufacturer. In any case the user is able to clearly identify the TOE hardware, its configuration and proof the validity of the certificate independently, meaning without involving the manufacturer.

The various blocking options, as well as the means used for the blocking, are done during the manufacturing process or at user premises. Entirely all means of blocking and the, for the blocking involved firmware respectively software parts, used at Infineon and/or the user premises, are subject of the evaluation. All resulting configurations of a TOE derivative are subject of the certificate. All resulting configurations are either at the predefined limits or within the predefined configuration ranges.

The firmware used for the TOE internal testing and TOE operation, the firmware and software parts exclusively used for the blocking, the parts of the firmware and software required for cryptographic support are part of the TOE and therefore part of the certification. The documents as described in section 2.2.4 and listed in *Table 1: Identification*, are supplied as user guidance.

Not part of the TOE and not part of the certification are:

• the Smartcard Embedded Software respectively user software, and

Security Target Lite 29 2015-10-30

• the piece of software running at user premises and collecting the BPU receipts coming from the TOE. This BPU software part is the commercially deemed part of the BPU software, not running on the TOE, but allowing refunding the customer, based on the collected user blocking information. The receipt from each blocked TOE is collected by this software – chip by chip.

#### 2.2.1 Hardware of the TOE

The hardware part of the TOE as defined in the Protection Profile PP [11] is comprised of:

### **Core System**

Proprietary dual CPU implementation being comparable to the 80251 microcontroller architecture from functional perspective and with enhanced MCS® 251 instruction set

**CACHE** with Post Failure Detection

Memory Encryption/Decryption Unit (MED) and Error Detection Unit (EDU)

Memory Management Unit (MMU)

#### Memories

SOLID FLASH™ NVM, the Electrically Erasable and Programmable Read Only Memory (EEPROM) implementing the Unified Channel Programming concept (UCP)

Read-Only Memory (ROM)

Random Access Memory (RAM)

## Peripherals

True Random Number Generator (TRNG) respectively

Physical True Random Number Generator (PTRNG)

Deterministic Random Number Generator (DRNG) respectively

Pseudo Random Number Generator (PRNG)

Watchdog and Timers

Universal Asynchronous Receiver/Transmitter (UART)

Checksum module (CRC)

RF interface (radio frequency power and signal interface)

Inter-integrated Circuit (I2C)

Software controlled Input Output (SWIO)

#### **Control**

**Advanced Power Management**

**CLK Unit**

Interrupt and Peripheral Event Channel Controller (ITP and PEC)

Interface Management Module (IMM)

User mode Security Life Control (UmSLC)

#### Coprocessors

Crypto2304T for asymmetric algorithms like RSA and EC (optionally blocked)

Symmetric Crypto Co-processor for DES and AES Standards (optionally blocked)

## **Security Peripherals**

Filters and Clk Detection

**Sensors and Detectors**

#### **Buses**

**Memory Bus**

Peripheral Bus

#### 2.2.2 Firmware and software of the TOE

The entire firmware of the TOE consists of different parts:

One part comprises the RMS and SA routines used for providing the chip resource management interface for the user. The routines are used for tearing save handling of the SOLID FLASH™ NVM, user testing of the security functions and error correction (Resource Management System, IC Dedicated Support Software in PP [11]). These routines are stored in a reserved area of the IFX ROM, while belonging patches (if any) are located in the SOLID FLASH™ NVM. If required also user software can be stored in the ROM.

The second part is the STS, consisting of test and initialization routines (Self-Test Software, IC Dedicated Test Software in PP [11]). The STS routines are stored in the ROM and the belonging patch is located in the access protected SOLID FLASH™ NVM area. The STS is not accessible for the user software.

The third part is the Flash Loader. This piece of software enables the download of the user software or parts of it to the SOLID FLASH™ NVM. The Flash Loader routines are stored in the especially protected test ROM but parts of it are also stored in the SOLID FLASH™ NVM. Depending on the order, the Flash Loader comes with the BPU-software enabling for TOE configuration at user premises. After completion of the download and/or final configuration of the TOE, and prior delivery to the end user, the user is obligated to lock the Flash Loader. Locking is the permanent deactivation of the Flash

Security Target Lite 31 2015-10-30

Loader meaning that if once locked it can no more be reactivated and used. Note that the Flash Loader routines are always present, but are disabled in case of the derivatives ordered without the software download option. Thus the user interface is identically in both cases — with and without Flash Loader on board - and consequently the related interface routines can be called in each of the derivatives.

The fourth part is the Mifare compatible Interface routines, called via RMS routines, if the related interface option is active. Note that these routines are always present, but are deactivated, in case of the derivatives coming without this option. Thus the user interface is identically in both cases and consequently the related interface routines can be called in each of the derivatives. In case the related interface routines are called in derivatives without this option, an error code is returned. In the other case the related function is performed.

All parts of the firmware above are combined together by the TOE generation process to a single file and stored then in the data files, the TOE is produced from. This comprises the firmware files for the ROM, where only Infineon Technologies AG has access, as well as the data to be flashed in the SOLID FLASH™ NVM.

The optional software part of the TOE consists of the RSA-, the EC, the SHA-2 and the Toolbox libraries.

The RSA library is used to provide a high level interface to the RSA cryptography implemented on the hardware component Crypto2304T and includes countermeasures against SPA, DPA and DFA attacks. The routines are used for the generation of RSA Key Pairs (RsaKeyGen), the RSA signature verification (RsaVerify), the RSA signature generation (RsaSign) and the RSA modulus recalculation (RsaModulus). The module provides the basic long number calculations (add, subtract, multiply, square with 1100 bit numbers) with high performance.