# Qualcomm SPU260 (v5.5) Security Target Lite

80-NU430-16 Rev. AA May 2, 2023

All Qualcomm products mentioned herein are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

Qualcomm and Snapdragon are trademarks or registered trademarks of Qualcomm Incorporated. Other product and brand names may be trademarks or registered trademarks of their respective owners.

This technical data may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A.

## **Revision history**

| Revision | Date        | Description              |

|----------|-------------|--------------------------|

| AA       | May 2, 2023 | Initial official release |

## **Contents**

| 1 Introduction to SPU260 (v5.5) Security Target |    |

|-------------------------------------------------|----|

| 1.1 Security Target reference                   | 7  |

| 1.2 TOE reference                               |    |

| 1.3 Conventions                                 |    |

| 1.4 Technical assistance                        |    |

|                                                 |    |

| 2 Target of Evaluation overview                 | 9  |

| 2.1 Target of Evaluation                        | 9  |

| 2.2 Non-TOE hardware and software               | 10 |

| 2.2.1 Non-TOE Software                          | 10 |

| 2.2.2 Non-TOE Hardware                          |    |

| 2.3 Security functions                          | 10 |

| 2.3.1 Internal Security functions               |    |

| 2.3.2 Cryptographic services (API)              |    |

| 2.3.3 Physical protection                       | 11 |

| O TOE In contact on                             | 40 |

| 3 TOE description                               |    |

| 3.1 TOE boundary and interface                  |    |

| 3.2 Scope of the TOE                            |    |

| 3.2.1 Overview                                  |    |

| 3.2.2 Hardware                                  |    |

| 3.2.3 Firmware, Software and Application        | 19 |

| 3.2.4 Package                                   |    |

| 3.2.5 Guidance documentation                    |    |

| 3.2.6 Forms of delivery                         |    |

| 3.2.7 TOE configuration                         |    |

| 3.2.8 TOE initialization                        |    |

| 3.2.9 TOE integration                           |    |

| 3.2.10 TOE Life-Cycle                           | 24 |

| 4 Conformance claims                            | 26 |

| 4.1 CC conformance claims                       | 26 |

| 4.2 PP claims                                   | 26 |

| 4.3 Package claims                              |    |

| 4.3.1 Conformance Claim Rationale               |    |

| 5 Occupitor and Law Jofferti                    |    |

| 5 Security problem definition                   |    |

| 5.1 Definition of assets                        |    |

| 5.2 Threats                                     | 28 |

| į.     | 5.3 Organizational security policies                                           | .30 |

|--------|--------------------------------------------------------------------------------|-----|

|        | 5.4 Assumptions                                                                |     |

| 6 Secu | rity objectives                                                                | 31  |

|        | 6.1 Security objectives for the TOE                                            |     |

|        | 6.2 Security objectives for the development and operational environment        |     |

|        | 6.3 Security objectives rationale                                              |     |

|        | •                                                                              |     |

|        | nded component definition                                                      |     |

| -      | 7.1 FMT_CMT Control over Management by TSF components                          |     |

|        | 7.1.1 Family behavior                                                          |     |

|        | 7.1.2 Component leveling                                                       |     |

|        | 7.1.3 Management: FMT_CMT.1                                                    |     |

|        | 7.1.4 Audit: FMT_CMT.17.1.5 FMT_CMT.1 management of TSF data by TSF components |     |

| -      | 7.1.3 FMT_CMT.1 management of 13F data by 13F components                       |     |

| •      | 7.2.1 Family behavior                                                          |     |

|        | 7.2.2 Component leveling                                                       |     |

|        | 7.2.3 Management: FDP_SDA.1                                                    |     |

|        | 7.2.4 Audit: FDP_SDA.1                                                         |     |

|        | 7.2.5 FDP_SDA.1 Stored Data Authenticity                                       | .38 |

| -      | 7.3 FDP_SDR Stored Data Replay protection                                      | .38 |

|        | 7.3.1 Family behavior                                                          |     |

|        | 7.3.2 Component leveling                                                       | .38 |

|        | 7.3.3 Management: FDP_SDR.1                                                    |     |

|        | 7.3.4 Audit: FDP_SDR.1                                                         |     |

|        | 7.3.5 FDP_SDR.1 Stored Data Replay Protection                                  | .38 |

| 8 Secu | rity requirements                                                              | 39  |

| 8      | 8.1 Security functional requirements                                           | .39 |

|        | 8.1.1 Security functional requirements from the body of the protection profi   |     |

|        |                                                                                |     |

|        | 8.1.2 Security functional requirements from augmentation packages              |     |

|        | 8.1.3 Security functional requirements beyond those in [ICPP]                  |     |

|        | 8.2 Security assurance requirements                                            |     |

| 8      | 8.3 Security requirements rationale                                            | .51 |

| 9 TOE  | summary specification                                                          | 57  |

|        | 9.1 TOE summary specification rationale                                        |     |

| `      | 9.1.1 Cryptographic services and random number generation                      |     |

|        | 9.1.2 Secure boot and secure update                                            |     |

|        | 9.1.3 Application manager                                                      |     |

|        | 9.1.4 Domain separation between applications executed by the TOE               | 64  |

|        | 9.1.5 Physical protection                                                      |     |

|        | 9.1.6 Access control and management (hardware)                                 |     |

|        | 9.1.7 Access control and management (operating system)                         |     |

|        | 9.1.8 Logical protection                                                       |     |

|        | 9.1.9 Production data and OTP handling                                         | 00  |

| 9.1.10 Life-Cycle Control        | 66 |

|----------------------------------|----|

| A Cryptographic mechanisms table | 67 |

| B References                     | 70 |

| B.1 Related documents            | 70 |

| B.2 Acronyms and terms           | 71 |

## **Figures**

| Figure 3-1 | TOE components and their interfaces to SoC | 13 |

|------------|--------------------------------------------|----|

| Figure 3-2 | TOE IC dedicated software components       | 15 |

| Figure 3-3 | TOE hardware components                    | 17 |

|            | TOE package                                |    |

|            | TOE Life-Cycle                             |    |

| Table      | s                                          |    |

|            |                                            |    |

|            | TOE components and identifiers             |    |

|            | SoC identifier                             |    |

| Table 5-1  | Security threats                           | 28 |

| Table 5-2  | Organization security policy               | 30 |

| Table 5-3  | Security assumptions                       | 30 |

| Table 6-1  | Security objectives for the TOE            | 31 |

| Table 6-2  | Security objectives for the environment    | 33 |

| Table 8-1  | Security Requirement vs Objectives mapping | 52 |

| Table 8-2  | Security Requirement dependencies          | 54 |

| Table 9-1  | TOE summary specification rationale        | 58 |

# 1 Introduction to SPU260 (v5.5) Security Target

This Security Target is defined for the Qualcomm® Secure Processor Unit (SPU260 (v5.5)), supported by Trusted Management Engine (TME), embedded in the SM8475 host System-on-Chip (SoC) combined with a double data rate (DDR) memory in a package-on-package (PoP) configuration and its corresponding IC dedicated software and associated documentation.

The hardware of TOE is comprised of the SPU and the TME subsystems. The IC dedicated software is comprised of a SPU Firmware, SPU Software, TME Firmware and TME Software, as described in 3.2 . The TOE is delivered together with the appropriate guidance documentation.

This Security Target includes claims derived from the Security IC Platform Protection Profile with Augmentation Packages [ICPP].

Because the Target of Evaluation (TOE) is not a usual smartcard IC, additional security functions of the hardware and the operating system (OS) have been added to this Security Target.

## 1.1 Security Target reference

"Qualcomm SPU260 (v5.5) Security Target Lite, 80-NU430-16 Rev. AA, Qualcomm Technologies, Inc."

#### **1.2 TOE reference**

The TOE described in this Security Target is named "Qualcomm Secure Processor Unit SPU260 (Version: 5.5) in SM8475 SoC (Qualcomm<sup>®</sup> Snapdragon™ 8+ Gen 1) with TME (Version: 1.0.5) and symmetric and asymmetric crypto support".

#### 1.3 Conventions

The security functional requirements (SFRs) have the following conventions:

- Assignments are underlined

- Selections are marked with squared brackets []

- Refinements are written in *italic*

- Iterations are identified with an extension of the Security Functional Requirement name

For example, the requirement in the Standard is written as follows:

The TSF shall perform [assignment: list of cryptographic operations] in accordance with a specified cryptographic algorithm [assignment: cryptographic algorithm] and cryptographic key sizes [assignment: cryptographic key sizes] that meet the following: [assignment: list of standards].

In this document, the requirement is written as follows:

The TSF shall perform message authentication code generation in accordance with a specified cryptographic algorithm CMAC using AES and cryptographic key sizes 128 bits, 256 bits that meet the following: FIPS 197 and NIST SP 800-38B.

#### 1.4 Technical assistance

For assistance or clarification on information in this document, open a technical support case at https://support.gualcomm.com/.

You will need to register for a Qualcomm ID account and your company must have support enabled to access our Case system.

Other systems and support resources are listed on <a href="https://qualcomm.com/support">https://qualcomm.com/support</a>.

If you need further assistance, you can send an email to qualcomm.support@qti.qualcomm.com.

## **2** Target of Evaluation overview

## 2.1 Target of Evaluation

The TOE is an integrated Secure Element, composed by two subsystems namely Secure Processor Unit (SPU) and TME, which are integrated in the SoC within a stacked DDR package on SoC package (package form factor is non-TOE). It is designed as a tamper resistant device providing secure storage and a secure execution environment for processing of sensitive data and for performing cryptographic operations using protected keys stored in its secure storage. Secure Elements can be used for multiple application areas that require a high level of security. Examples are as follows:

- User authentication and password storage

- Content protection

- Payment

- Subscriber Identity Module (SIM)

- Storage and management of digital identities

- Secure key storage

- Root of trust

- Secure Storage of sensitive user data (for example health care records)

The TOE has dedicated interfaces to other components of the SoC, which allow those components to communicate with the TOE and request services from the TOE.

The TOE is comprised of a hardware layer and IC dedicated software providing interfaces for application developers.

The TOE will allow for dedicated applications to execute on the OS of the TOE to provide security services as listed above. Those applications are not part of the TOE, but the TOE OS provides services to verify the integrity and authenticity of such applications using digital signatures.

The TOE communicates with the other components of the SoC either using shared memory or using shared Configuration and Status Registers (SP-sCSR), interrupts, and power control messages.

The hardware of the TOE is internally structured into three main units:

- The Secure Central Processing unit, which performs the general operations of the TSF.

- The Crypto Management unit, which performs the cryptographic operations and generates, manages, and protects keys.

- The TME subsystem unit, of which the involvement in the TOE is limited to support the SPU during the secure boot process.

For a more detailed description of those units, their functions and how they are internally structured, see section 3.1 on TOE definition.

#### 2.2 Non-TOE hardware and software

#### 2.2.1 Non-TOE Software

The TOE is embedded onto Qualcomm Snapdragon<sup>™</sup> 8+ Gen 1, used in mobile applications. Snapdragon<sup>™</sup> 8+ Gen 1 comprises a High Level Operating system (HLOS, such as Android) that is required for the TOE to boot and properly communicate with the rest of the Hardware and Software. Only this way the TOE is in the certified configuration.

#### 2.2.2 Non-TOE Hardware

The TOE requires presence of the host SoC (Snapdragon<sup>™</sup> 8+ Gen 1), DDR (external RAM), sMMU as well as NVM to be functional. The final device in the field consists of a PoP. One package contains the SoC integrating the TOE hardware and the other package contains the DDR. The TOE software image is stored encrypted in NVM. DDR is referred as an external RAM, which is required to load and execute the SPU software on the SPU.

## 2.3 Security functions

## 2.3.1 Internal Security functions

The TOE implements the following internal Security functions:

- Access control to the various memories (OTP, RAM, ROM) and peripherals

- Access control to keys managed in hardware through enforcement of key policy

- Secure boot and secure loading of TOE software stored outside the TOE using the TOE root of trust (ROM code and TME subsystem)

- Protection of User Data stored outside the TOE

- Secure loading of user applications stored outside the TOE

- Secure update mechanism of the TOE software or applications

- Domain separation between applications executed by the TOE (for both user and system applications)

- Anti-replay island and software freshness protection

#### 2.3.2 Cryptographic services (API)

Note: This section is an overview. See functional security requirements descriptions for details on each algorithm and key type/size.

The TOE provides cryptographic services using the support of the Crypto Management Unit. Services provided through the API for user applications are as follows:

- Generation of random numbers (used for key generation)

- Secure key storage providing the possibility to have keys stored in the SP-CMU that are not readable by the SP-CPU. The SP-CPU can only request to perform cryptographic operations using those keys.

- Secure key generation and zeroization

- Symmetric encryption and decryption using the following:

- AES with 128 bit and 256 bit keys

- TDES with 112 bit and 168 bit keys

- Hash functions: SHA-1, SHA-256, SHA-384, SHA-512

- HMAC using keys up to 512 bit length and using SHA-1, SHA-256, SHA-384 or SHA-512

- CMAC with AES using 128 bit and 256 bit keys

- Asymmetric cryptographic operations:

- RSA 1024 bit and 2048 bit

- □ Elliptic curves cryptography with NIST P-192/224/256/384/521, Brainpool P-192/224/256/320/384/512 non-twisted (r1) and Curve25519 curves.

## 2.3.3 Physical protection

The TOE provides a number of functions and features that are designed to counter physical attacks. Those include the following:

- Memory scrambling/memory encryption

- Side-channel analysis countermeasures

- Fault attacks sensors and countermeasures

- Memory/registers integrity checking

## **3** TOE description

## 3.1 TOE boundary and interface

The TOE are two independent subsystems that will be integrated in the SM8475 SoC in a manner that is agnostic to the TOE hardware and IC dedicated software implementation details. The TOE serves as an independent Root of Trust within the SoC. It does not rely on any external entity for any security enforcement, allowing it to be evaluated as a separate entity. Even though NVM, DDR and package form factor are considered non-TOE hardware, they do not enforce any security functionality but the TOE relies on them for TOE functionality. The TOE has also its own ROM code and a dedicated TME subsystem for secure boot operations (other TME functions different than those related to secure boot operations are considered SFR-non-interfering).

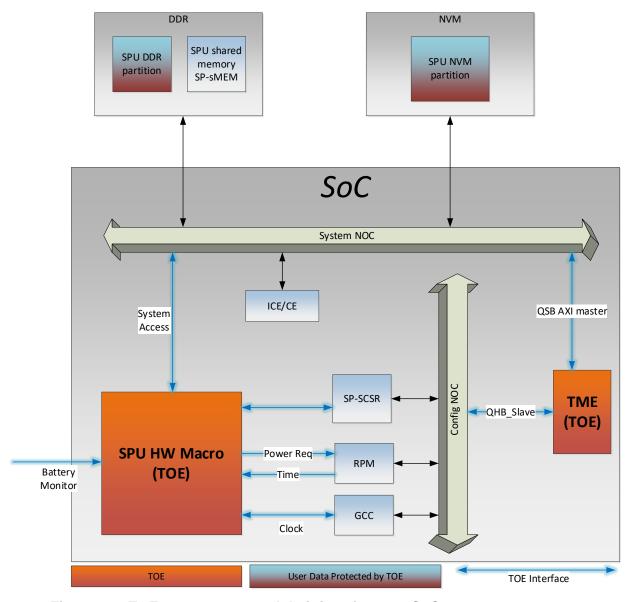

The TOE and its hardware interfaces to the SoC into which it is integrated are shown in the following figure.

The TOE Hardware interfaces are:

- Battery Monitor (indicates when power is lost)

- System Access to allow SPU to read/write in the SPU shared memory in DDR (SP-sMEM) as well as in SPU protected memory partitions in DDR and non-volatile memory (NVM). This interface is also used by the SPU to communicate with other peripherals of the SoC such as GPIO.

- QSB AXI master between TME and System NOC to enable the communication between the TME subsystem and the SPU for secure boot operations.

- QHB\_Slave between TME and Config NOC.

- Interface to read/write SP-sCSR with the SoC. These CSRs are among other things used as doorbell for communication between the SPU and the rest of the SoC and in particular with the TME for secure boot operations.

- Interface to the RPM (Resource and Power Manager) module to provide SPU power requirement and for receiving time data from RPM.

- Interface to the Clock Controller (GCC) to provide clock requirement and receive external clock and reset signal for the entire chip, including the SPU.

As indicated earlier, the TOE provides a TSF to cryptographically protect User Data before storage in an SPU DDR partition or SPU NVM partition. This TSF also ensures that User Data read from these locations are trustworthy before processing them internally.

Figure 3-1 TOE components and their interfaces to SoC

The TOE Software interface consist in Application Programming interfaces providing:

- Communication services

- External Memory storage (read/write) services

- Cryptographic services

The TOE communicates with the other components of the SoC via the SPU shared memory, the SPU shared Configuration and Status Registers.

## 3.2 Scope of the TOE

#### 3.2.1 Overview

The TOE is composed of:

- SPU Hardware: a hardmacro synthetized independently of rest of SoC and integrated as a black box

- SPU IC dedicated software: is a superset of code formed by SPU Firmware (ROM code) and SPU Software (RAM code loaded from NVM). The code belonging to OS and CryptoLib is formed by different pieces of these both sources.

- SPU Firmware:

- Primary Boot Loader (PBL): includes part of the low level cryptography of the CryptoLib and is used to load the encrypted software part of the SPU after being enabled by TME, as described in section 3.2.3.

- Mission ROM: Part of OS, which includes drivers and another part of the low level cryptography of the CryptoLib.

- □ SPU Software:

- MCP: Part of OS, which provides APIs and services for the SPU system applications and the user applications.

- SPU System Applications: Part of OS, which provides additional TOE functionalities that are not packaged in the SPU Firmware or MCP.

- User applications: They are considered as Security IC Embedded Software, and therefore out of the scope of the TOE. Note that the user applications can only access HW features via the APIs and services from MCP and therefore does not have direct interaction with firmware.

- TME Hardware: a separated subsystem integrated in the SoC but outside the SPU which communicates with the SPU during secure boot process.

- TME IC dedicated software: as part of the TOE IC dedicated software and a superset of code formed by TME Firmware (ROM code) and TME Software (RAM code loaded from NVM). It is in charge of giving support to the SPU in the early stages of the secure boot process (other functions of the TME are considered as SFR-non-interfering). Its parts are the following:

- TME Firmware:

- TME Mission ROM: stored in TME CPU ROM, includes drivers and low level cryptography.

- TME Sequencer Firmware: stored in TME Sequencer ROM, which verifies the TME Sequencer Software in TME Sequencer RAM prior to the TME Sequencer Software is executed.

- TME PBL: stored in TME CPU ROM, includes part of the low level cryptography and is used to authenticate the TME Core Software image prior to the TME Core Software is executed.

- TME Software

- TME Sequencer Software: manages the communication with the registers and clocks.

- TME Core Software: supports the secure boot of the SPU.

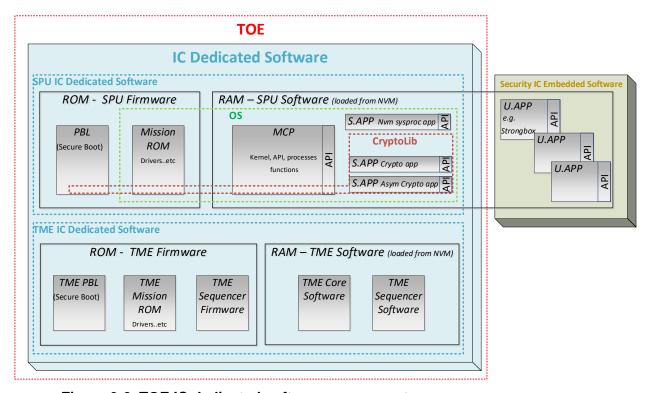

The following figure shows the TOE IC dedicated software components of the TOE as well as the Application Programming Interface of the TOE as is used by the user application running in the TOE. Note that in Figure 3-2, SPU System Application and User Application are referred as S.APP and U.APP, respectively.

Figure 3-2 TOE IC dedicated software components

The OS is composed of MCP, system applications (cryptoapp, asym\_cryptoapp, nvm\_sysproc) and Mission ROM. The CryptoLib is composed of cryptography relevant part of PBL, cryptography relevant part of Mission ROM, cryptography relevant part of MCP and system applications (cryptoapp and asym\_cryptoapp).

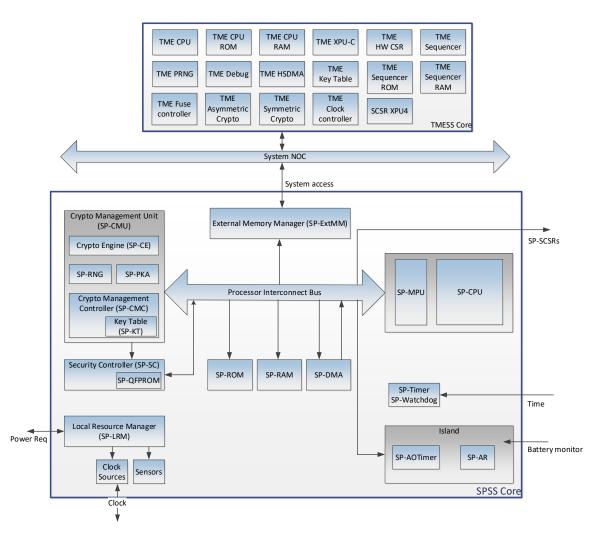

#### 3.2.2 Hardware

The physical boundary of the TOE includes the TOE hardware which consists of the following components:

- For SPU subsystem (SPSS)

- Secure Central Processing Unit (SP-CPU), which executes the main code of the SPU.

- Memory: SP-RAM (for kernel, applications stacks) and SP-ROM (for the PBL image and mission ROM).

- Memory Protection Unit (SP-MPU), which is responsible for controlling access to memory (SP-ROM and SP-RAM) and the DMA controller (SP-DMA)

- Crypto Management Unit (SP-CMU), which provides support for random number generation and key generation (SP-RNG) as well as HW accelerated hash, symmetric and asymmetric cryptographic functions (SP-CE and SP-PKA). It also holds a Crypto Management Controller (SP-CMC) in which Key Table (SP-KT) exists.

- Processor Interconnect Bus, which is used for data exchange between the SP-CPU and the SP-CMU.

- Local Resource Manager (SP-LRM), which provides the interface to the Clock Source, the reset line and the interface to the Sensors (voltage, temperature, frequency etc.).

- Security Controller (SP-SC) Block, which holds the Qualcomm Fuse-Programmable Read-Only Memory (SP-QFPROM) area including keys that the SP-CPU can request to be used by the SP-CMU but cannot read directly.

- SP-Timer and SP-Watchdog, used to provide timer functionality for the TOE independent from other timers within the SoC.

- □ The always-on Island that contains the part of the Anti-Replay controller (SP-AR) and the Always-On Timer (SP-AOTimer).

- The External Memory Manager (SP-ExtMM) providing read/write capabilities to TOE external memory.

#### For TME subsystem (TMESS)

- TME CPU, hardened CPU to execute the TME PBL, TME Mission ROM and TME Core Software. It is also the entry point into TME (slave) and includes the AXI master to the SNoC, with address remappers.

- □ TME CPU ROM and TME CPU RAM, memories used by TME CPU.

- TME Sequencer, module to execute TME Sequencer Firmware and TME Sequencer Software which controls all the resources under TME HW layer.

- TME Sequencer ROM and TME Sequencer RAM, memories used by TME Sequencer.

- □ TME XPU-C, module containing the access control protection units.

- □ TME PRNG, module for hardware-only random number generator.

- □ TME Debug, debug module for debugging purposes.

- TME HSDMA, High Speed DMA with FIFOs.

- □ TME Key Table, which Store keys used by the crypto engines on TME.

- □ TME Hardware CSR, register map used by the CPU or JTAG to execute commands on the sequencer.

- TME Fuse controller, module which contains the QFPROM.

- TME Asymmetric Crypto, which provides ECC & RSA based asymmetric cryptography services to TME CPU and SoC through the SEQ.

- TME Symmetric Crypto, which performs symmetric cryptographic operations for the sequencer.

- TME Clock Controller, module which implements the control of the clocks.

- SCSR XPU4, module which controls the access to SCSR.

Figure 3-3 TOE hardware components

#### 3.2.2.1 SPU subsystem

#### 3.2.2.1.1 SP-CPU

The SP-CPU is the main processing unit of the SPU. It executes the general firmware and software of the TOE. The SP-CPU provides memory protection that allows the implementation of a secure OS that separates unprivileged applications from each other and allows protection of critical resources from direct access by applications without using the OS services that control access to such critical resources.

#### 3.2.2.1.2 SP-MPU

The memory protection unit of the SPU (SP-MPU) is responsible for controlling access to memory (SP-ROM and SP-RAM) and the DMA controller (SP-DMA) in accordance with the access control attributes. It is programmed by the SP-CPU from its privileged mode, allowing the OS running on the SP-CPU to protect memory areas from direct access by applications and protect memory areas assigned to one application from direct access by another application. The SP-MPU is supplemented by two permission checkers embedded in the SP-RAM and SP-ROM.

#### 3.2.2.1.3 SP-CMU

The SP-CMU is a separate subsystem within the SPU that is responsible for the cryptographic operations performed by the SPU as well as the generation and protection of key material used for those operations. The SP-CMU subsystem actually acts like a separate hardware security module in a general purpose operating environment. It consists of the following:

- Crypto engine (SP-CE) as the central processing unit of the SP-CMU (which also includes the hardware implementation of the cryptographic coprocessors: AES, SHA-1 and SHA-256).

- Random number generation unit (SP-RNG), which consists of two physical noise sources and a DRBG.

- Hardware support for accelerating asymmetric crypto operations (SP-PKA).

- Crypto Management Controller (SP-CMC), which manages the Key Table (SP-KT) including the transfer of keys to the SP-KT.

The SP-CMU is programmed by the SP-CPU, which can request operations such as key generation, loading the key, or performing cryptographic operations; the SP-CPU does not have access to the keys themselves that are managed by the SP-CMC (unless the key attributes allow the key to be exported in clear outside the SP-CMU subsystem). The SP-CMC manages the keys stored in the SP-KT, which are the keys private to the SPU.

#### 3.2.2.1.4 SP-SC

The security control component (SP-SC) contains the SP-QFPROM (also called as OTP) and is responsible for controlling access to OTP areas there. This includes protection of areas that are write-protected and control access of the SP-CPU to allow it to only access dedicated OTP items that are not indicated as read-protected. Some secret data stored in OTP are stored in encrypted form.

#### 3.2.2.1.5 SP-LRM

The SP-LRM is responsible for interrupt handling and management of the SPU. The sensors that detect operational problems, faults, or potential attacks are connected to the SP-LRM and cause an interrupt when they detect a problem. The SP-LRM passes the interrupt to the SP-CPU for handling and requires the SP-CPU to clear the interrupt, indicating that it has received and processed the interrupt. Alternatively, the SP-LRM can be configured to perform a cold reset upon specific sensors detection.

Note that internal interrupts of the SP-CPU (such as system tick time expiration, SP-MPU permission error, and privilege exception) are handled directly by the SP-CPU and not by the SP-LRM, but an interrupt caused by the SP-Timer is handled by the SP-LRM.

#### 3.2.2.2 TME subsystem

#### 3.2.2.2.1 TME Subsystem Core

The TME subsystem is a separated part of the TOE but within the SoC and in charge of the early stages of the secure boot process. It is composed by the TME CPU which runs the TME PBL, TME Core Firmware and TME Core Software in its own RAM and the TME Sequencer, which runs the TME Sequencer Firmware and TME Sequencer Software. The TME Sequencer drives the steps during the secure boot while the TME CPU is finally in charge of bringing the SPU out of reset in this process. Only these modules related to secure boot are considered involved in the security functionality as SFR-supporting.

#### 3.2.3 Firmware, Software and Application

#### 3.2.3.1 Related to SPU

The SPU-PBL and OS with the software API are considered as logical boundary of the TOE to user application. The OS manages the access to the services provided by the TOE, implements software countermeasures and controls the user applications.

The TOE OS consists of:

- The Mission ROM (stored in SP-ROM)

- The software (loaded from NVM and stored in SP-RAM and DDR)

- MCP image (in SP-RAM)

- System applications (in DDR)

- cryptoapp

- asym\_cryptoapp

- nvm\_sysproc

In a nutshell, the SPU-PBL in SPU Firmware loads MCP which loads system applications.

The TOE contains the firmware in SP-ROM that is used for the secure boot process (supported by TME). In addition, part of the SPU Firmware contains drivers that are used in operational mode by the loaded SPU Software (after the secure boot).

The TOE also contains the SPU Software, MCP, which is stored, signed and encrypted in external non-volatile memory and loaded into SP-RAM at runtime by the PBL. The PBL verifies the signature and decrypts the software each time before the MCP is loaded and executed by the SP-CPU.

The OS is formed by the MCP, the system applications and the Mission ROM. The OS is running on the SP-CPU and provides services to user applications loaded for the SP-CPU. The OS verifies the integrity and authenticity and enforces confidentiality of any applications loaded to the TOE including system applications.

The MCP image and the Applications are stored in external memory and can be updated by downloading a newer version in the external memory. A set of rollback counters prevent the TOE from loading an older version of MCP or an application.

The OS is also responsible to separate applications executing on it from each other and control that an application uses only those services and objects it is supposed to use (as defined in the manifest of the downloaded and signed application package). This OS is part of the TOE and implements some TSF.

The system applications, as part of OS, are stored in external non-volatile memory and are loaded into DDR at runtime by the aforementioned MCP. The TOE contains three system applications:

- Cryptoapp: implements the RSA key generation service.

- Asym\_cryptoapp: implements additional asymmetric cryptography services and the corresponding API.

- Nvm\_sysproc: implements nvm system process.

The OS provide the following services to User applications via APIs:

- Cryptographic services (AES CMAC, Hashing and message authentication codes) with keys either held as retained keys within the SP-CMU (in the SP-KT) or with keys provided by the application. If retained keys are used, the OS verifies that the application is allowed to use those keys and if they are used in accordance with the key attributes. In addition, the TOE provides random number generation services.

- Cryptographic services (AES, TDES, ECDSA, ECDH and RSA) with keys provided by the application.

- NVM storage for User data. User data is stored (in external DDR/NVM) encrypted, authenticated and protected against replay. The TOE maintains a unique key for each application that is used for these cryptographic operations.

- Communication services with external entities (for example Modem sub-system, HLOS or Trusted Execution Environment).

- Application loading services.

#### 3.2.3.2 Related to TME

The TME PBL, TME Mission ROM, TME Sequencer Firmware, TME Sequencer Software and TME Core Software are considered as logical boundary of the TOE from the side of the TME subsystem.

The logical scope components are:

- TME PBL (stored in TME CPU ROM) which authenticates the TME Core Software image.

- TME Mission ROM (stored in TME CPU ROM) includes drivers and low level cryptography.

- TME Sequencer Firmware (stored in TME Sequencer ROM) which verifies the TME Sequencer Software image.

- TME Sequencer Software (stored in NVM and is loaded to TME Sequencer RAM) which allows access to the underlying hardware.

- TME Core Software, (stored in NVM and is loaded to TME CPU RAM) which is in charge of taking SPU out of reset.

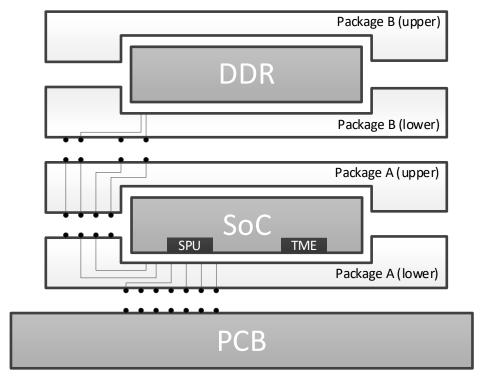

#### 3.2.4 Package

The final device in the field consists of a PoP. One package contains the SoC integrating the TOE hardware and the other package contains the DDR that is needed for SPU to be operational and in a certified configuration. The package is part of TOE operational environment.

The package in which the TOE is delivered is shown in an abstracted way, not to scale and without all connections in the following figure. The figure illustrates highlighted in dark, the physical boundary of the TOE within the final PoP package, not included in the TOE.

PoP solution consists in:

- The Package A containing the SoC bare die integrating the TOE hardware.

- The Package B containing the DDR bare die required for the system to work.

The SoC is integrated into Package A during phase 4 (see 3.2.10).

The package B is stacked on Package A during phase 6 (see 3.2.10).

Figure 3-4 TOE package

#### 3.2.5 Guidance documentation

The API for the use of the Services of the Secure Processor as well as associated guidance are provided with the software development kit..

#### 3.2.6 Forms of delivery

The TOE comprises all items that listed in *Table 3-1*.

The TOE hardware and firmware including the personalization data (in SP-QFPROM) will be delivered in the form of a partly packaged SoC to the OEMs to integrate the SoC into his devices.

The integration includes a step of adding a DDR package on top of the partly packaged SoC. This is called a PoP.

In addition, the OEMs will receive the TOE software (MCP image, system applications and TME Core Software image) as part of an overall Qualcomm SW package for the SoC. Qualcomm provides customers access to the Agile system that can be used to download the SW package.

The TOE software will be loaded by the OEMs in the device NVM.

Also the guidance documents listed in *Table 3-1* can be downloaded from the database provided in Agile.

Delivery protection for all TOE components is covered by ALC\_DEL and ALC\_DVS.

#### 3.2.7 TOE configuration

The following table describes the TOE components and the identifiers:

Table 3-1 TOE components and identifiers

| Item Type | Item                                           | Identifier               | Form of<br>Delivery                                                 |

|-----------|------------------------------------------------|--------------------------|---------------------------------------------------------------------|

| Hardware  | SPU hard macro embedded in SM8475 SoC          | 5.5                      | Die in package<br>A as in Figure                                    |

|           | TME hard macro embedded in SM8475 SoC          | 1.0.5                    | 3-4                                                                 |

|           | Foundry ID embedded in SM8475<br>SoC           | 0                        |                                                                     |

| Firmware  | SPU ROM code PBL Mission ROM                   | 77100000                 | Included in SPU<br>hard macro<br>ROM                                |

|           | TME CPU ROM code  TME PBL  TME Mission ROM     | Linked to TME hard macro | Included in TME<br>CPU hard<br>macro ROM as<br>part of TME HW       |

|           | TME Sequencer ROM code  TME Sequencer Firmware | Linked to TME hard macro | Included in TME<br>Sequencer hard<br>macro ROM as<br>part of TME HW |

| Item Type | Item                                                                                                            | Identifier                                                                                                                                                                                                                                                                                                                             | Form of<br>Delivery                 |

|-----------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Software  | SPU Software image, which includes MCP and following system applications:  cryptoapp asym_cryptoapp nvm_sysproc | SPSS.A1.1.6.1-00032-PALIMA-1                                                                                                                                                                                                                                                                                                           | Software image encrypted and signed |

|           | TME Sequencer Software image                                                                                    | ■ Build release string  ■ 53 45 51 5F 46 57 5F 52 45 4C 45 41 53 45 5F 42 55 49 4C 44 5F 56 45 52 53 49 4F 4E 5F 53 54 52 49 4E 47 3D 72 39 ("SEQ_FW_RELEASE_BUILD_VERSION_STRING=r9" in ASCII)                                                                                                                                        | Software image signed               |

|           | TME Core Software image                                                                                         | Build time string  4D 61 79 20 30 35 20 32 30 32 32 20 61 74 20 31 36 3A 30 32 3A 34 34 ("May 05 2022 at 16:02:44" in ASCII)  Version string  73 73 67 2E 74 6D 65 66 77 2E 31 2E 30 2E 31 2D 30 30 32 39 39 2D 72 65 6C 65 61 73 65 ("ssg.tmefw.1.0.1-00299-release" in ASCII)  Chipset string  57 61 69 70 69 6F ("Waipio" in ASCII) | Software image signed               |

| Document  | Secure Processor Unit (SPU) –<br>Anti-replay Island (ARI) Overview<br>for SM8450/SM8475                         | 80-11140-16, Revision AC                                                                                                                                                                                                                                                                                                               | PDF                                 |

|           | Qualcomm® Secure Processing<br>Unit Enablement for<br>SM8450/SM8475 Devices – User<br>Guide                     | 80-PV345-150, Revision AG                                                                                                                                                                                                                                                                                                              | PDF                                 |

|           | SM8450/SM8475 Security<br>Guidance for Secure Processing<br>Unit Application Developers                         | 80-PV345-152, Revision AE                                                                                                                                                                                                                                                                                                              | PDF                                 |

|           | SM8450/SM8475 Secure Boot<br>Enablement                                                                         | 80-PV345-14, Revision AF                                                                                                                                                                                                                                                                                                               | PDF                                 |

|           | SM8450/SM8475 Secure<br>Processor Unit SDK – API<br>Reference                                                   | 80-PV579-11, Revision AE                                                                                                                                                                                                                                                                                                               | PDF                                 |

|           | Qualcomm® Snapdragon™ Secure<br>Processing Unit (SPU) Application<br>Development User Guide                     | 80-NU430-7, Revision AB                                                                                                                                                                                                                                                                                                                | PDF                                 |

|           | SMT Assembly Guidelines                                                                                         | SM80-P0982-1, Revision E                                                                                                                                                                                                                                                                                                               | PDF                                 |

TOE is integrated into SoC of which the identifier is listed below:

Table 3-2 SoC identifier

| Item       | Identifier |

|------------|------------|

| SM8475 SoC | A0080000   |

#### 3.2.8 TOE initialization

The TOE is provisioned with individual keys and transitions to operational state during Final Test in Outsourced Semiconductor Assembly and Test (OSAT) premises.

The TOE can only boot fully after it has been integrated in a device containing the Software (MCP image and TME Sequencer / Core Software images) during the product integration phase by the OEMs.

After composite product integration and during operational usage the TOE performs the following action upon boot:

- TME bring up SPU

- Life-Cycle control

- SPU260 (v5.5) configuration

- Verify signature and decrypt the MCP image in SP-RAM

- Execute MCP

- Verify signature and decrypt the MCP image to load the system applications in DDR

## **3.2.9 TOE integration**

The TOE is an integrated part of a larger SoC that itself is intended to be integrated into mobile or other devices.

## 3.2.10 TOE Life-Cycle

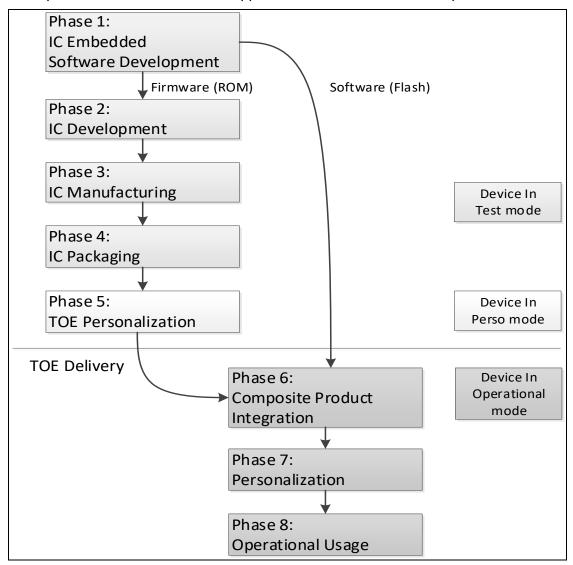

The Life-Cycle of the TOE has been modified (refined with additional phase) compared to [ICPP] to match our TOE Life-Cycle.

The Life-Cycle control of the TOE ensures that a device in Test mode cannot run the TOE software and limits access to the TOE firmware (to the minimal set of code required to boot).

The Life-Cycle control of the TOE ensures that the device is in Perso mode before TOE Personalization (phase 5) is performed, where initialization and pre-personalization happens. Initialization includes static data provisioning while pre-personalization includes per chip data provisioning (such as keys)

The Life-Cycle control of the TOE ensures that TOE data (stored during phase 5) and user data (stored during phase 7) are protected in Operational mode.

The process of developing and manufacturing a composite product that contains the TOE is shown in the following figure.

The Firmware and Software development is done as part of the TOE development and the Firmware is internally delivered for the integration into the ROM.

The IC packaging phase embeds the SoC into PCBs on both sides that allow the addition of the DDR and the integration into the final product. DDR addition and integration into the final product is done in Phase 6.

TOE personalization includes the provisioning of keys that allow customers to perform further personalization of their SPU applications while the TOE is in Operational mode.

Figure 3-5 TOE Life-Cycle

## 4 Conformance claims

#### 4.1 CC conformance claims

This Security Target and the TOE claim conformance to *Common Criteria for Information Technology Security Evaluation*, Parts 1, 2, and 3, Version 3.1, Revision 5, which is referred to in this document as *[CC]*.

The Security Target conformance claimed is: Part 1 conformant, Part 2 extended, Part 3 conformant.

#### 4.2 PP claims

This Security Target claims strict conformance to Security IC Platform Protection Profile with Augmentation Packages, Version 1.0 (BSI-CC-PP-0084-2014), which is referred to in this document as [ICPP].

## 4.3 Package claims

The packages for AES and Hash functions from [ICPP] have been included.

The Security Target claims conformance to EAL4 augmented by ALC\_DVS.2 and AVA\_VAN.5.

#### 4.3.1 Conformance Claim Rationale

The TOE specified in this Security Target is a self-sufficient component of a packaged Qualcomm Snapdragon System-on-Chip (SoC). Apart from access to memory, power supply and the connectivity to consumers of the TOE functionality, the remainder of the SoC does not support any aspect of the operation of the TOE.

The TOE can therefore be regarded as a Security Integrated Circuit which implements all functional aspects specified by the protection profile. The TOE provides different types of cryptographic services to external entities, stores and generates keys which can be used for different cryptographic operations. The keys stored and processed by the TOE are protected against logical or physical attacks.

In addition, the development and production Life-Cycle specified by the protection profile is compatible with the one applicable to the TOE.

This allows the conclusion that the protection profile with its intended use cases is applicable to the TOE.

## **5** Security problem definition

#### 5.1 Definition of assets

The assets to be protected are as follows:

- User data stored inside the SPU, or processed by the SPU

- User data stored outside the TOE while under the control of the TOE

- TSF data used internally by the TOE such as internal encryption keys, SPU Firmware...etc.

- Security IC Embedded Software (user applications), being stored and being executed

- Security services provided by the SPU to the user applications, executed in the SPU

Components of the SoC that are not part of the TOE are considered external entities and they can communicate with the TOE in a similar way an external entity communicates with a smart card. The communication between those components and the SPU is via the SP-sCSR, interrupts, and the shared memory areas. The SP-sCSR act as mailboxes where the other components send requests to the SPU, and the shared memory areas are used for bulk data transfer required to process those requests.

More precisely, the TOE assets that require protection are only in SPU, listed as follows:

- Root keys

- Keys derived from root keys

- Revision

- Life-Cycle state data

- Code execution control

- Code and data integrity, authenticity and confidentiality (load and runtime)

- Debug/Test mode/interface

## 5.2 Threats

The following threats are defined in [ICPP].

**Table 5-1 Security threats**

| Threat                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T.Leak-Inherent                                                   | Inherent Information Leakage An attacker may exploit information, which is leaked from the TOE during usage of the Security IC, to disclose confidential user data as part of the assets.                                                                                                                                                                                                                                                                                                                                              |

| T.Phys-Probing                                                    | Physical Probing An attacker may perform physical probing of the TOE (i) to disclose user data while stored in protected memory areas, (ii) to disclose/reconstruct user data while processed, or (iii) to disclose other critical information about the operation of the TOE to enable attacks disclosing or manipulating user data of the Composite TOE or the Security IC Embedded Software.                                                                                                                                        |

| T.Malfunction                                                     | Malfunction due to Environmental Stress An attacker may cause a malfunction of TSF or the Security IC Embedded Software by applying environmental stress to (i) modify security services of the TOE, (ii) modify functions of the Security IC Embedded Software, or (iii) deactivate or affect security mechanisms of the TOE to enable attacks disclosing or manipulating user data of the Composite TOE or the Security IC Embedded Software. This may be achieved by operating the Security IC outside normal operating conditions. |

| T.Phys-Manipulation                                               | Physical Manipulation An attacker may physically modify the Security IC to (i) modify user data of the Composite TOE, (ii) modify the Security IC Embedded Software, (iii) modify or deactivate security services of the TOE, or (iv) modify security mechanisms of the TOE to enable attacks disclosing or manipulating user data of the Composite TOE or the Security IC Embedded Software.                                                                                                                                          |

| T.Leak-Forced                                                     | Information Leakage An attacker may exploit information, which is leaked from the TOE during usage of the Security IC, to disclose confidential user data of the Composite TOE as part of the assets even if the information leakage is not inherent but caused by the attacker.                                                                                                                                                                                                                                                       |

| T.Abuse-Func                                                      | Abuse of Functionality An attacker may use functions of the TOE which may not be used after TOE Delivery to (i) disclose or manipulate user data of the Composite TOE, (ii) manipulate (explore, bypass, deactivate, or change) security services of the TOE, or (iii) manipulate (explore, bypass, deactivate, or change) functions of the Security IC Embedded Software, or (iv) enable an attack disclosing or manipulating user data of the Composite TOE or the Security IC Embedded Software.                                    |

| T.RND                                                             | Deficiency of Random Numbers  An attacker may predict or obtain information about random numbers generated by the TOE security service, for instance, because of a lack of entropy of the random numbers provided.                                                                                                                                                                                                                                                                                                                     |

| The following threats are not part of [ICPP] and have been added: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| T.Boot-Compromise                                                 | Compromising the Boot Functionality An attacker might attempt to interfere with the boot process by attempting to boot TSF software not authorized by the TOE.                                                                                                                                                                                                                                                                                                                                                                         |

| T.CONFID-TSF-CODE                                                 | The attacker executes an application without authorization to disclose the TSF software.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Threat                                                                                                                           | Description                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| T.CONFID-APPLI- DATA  The attacker executes an application without authorization to disclose a belonging to another application. |                                                                                                      |

| T.CONFID-TSF-DATA                                                                                                                | The attacker executes an application without authorization to disclose data belonging to the TSF.    |

| T.INTEG-APPLI-<br>CODE                                                                                                           | The attacker executes an application to alter (part of) its own or another application's code.       |

| T.INTEG-TSF-CODE                                                                                                                 | The attacker executes an application to alter (part of) the TSF software.                            |

| T.INTEG-APPLI-DATA                                                                                                               | The attacker executes an application to alter (part of) another application's data.                  |

| T.INTEG-TSF-DATA                                                                                                                 | The attacker executes an application to alter (part of) TSF data.                                    |

| T.AUTH-TSF-DATA                                                                                                                  | The attacker replaces (part of) TSF data with (part of) TSF data from another device                 |

| T.AUTH-APPLI-DATA                                                                                                                | The attacker replaces (part of) application data with (part of) application data from another device |

| T.RBP-TSF-DATA                                                                                                                   | The attacker performs a replay operation on (part of) TSF data (replay an older version)             |

| T.RBP-APPLI-DATA                                                                                                                 | The attacker performs a replay operation on (part of) application data (replay an older version)     |

Threat agents that must be considered are as follows:

- Non-TOE Software executing as nonprivileged software on the SP-CPU, attempting to attack the functionality of the TOE or gain information by observing the behavior of the TOE. Only software whose manifest is vetted by Qualcomm can be loaded into the TOE. Qualcomm vets the software developer and controls privileges of the software by the manifest. To keep the evaluation to a reasonable effort, such software components are not included into the TOE.

- Hardware or software executing on other components of the SoC, attempting to attack the functionality of the TOE or gain information by observing the behavior of the TOE.

- External entities accessing the SoC via its external interfaces.

- External attackers that physically probe the TOE.

- External attackers that attempt to gain access to TSF or user data (critical information) by observing the behavior of the TOE.

## 5.3 Organizational security policies

The following organizational security policy is defined in [ICPP].

Table 5-2 Organization security policy

| Policy                  | Description                                                                                                                                                                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P.Process-TOE           | Identification during TOE Development and Production  An accurate identification must be established for the TOE. This requires that each instantiation of the TOE carries this unique identification.                                                                                                   |

| P.Crypto-Service        | Cryptographic services of the TOE The TOE provides secure hardware based cryptographic services for the IC Embedded Software.                                                                                                                                                                            |

|                         | Application Note: the following crypto services are supported by hardware: AES, SHA-1, SHA-256, SHA-384, SHA-512, HMAC, CMAC AES and KDF and the asymmetric accelerator for ECDH/ECDSA, RSA_SIGN and RSA_ENC                                                                                             |

|                         | (for all modes, please refer to appendix A).                                                                                                                                                                                                                                                             |

| Two organizational secu | rity policies have been added that is not included in [ICPP]:                                                                                                                                                                                                                                            |

| P.Least-Privilege       | Least Privilege for TSF Components  The TSF itself is structured into a number of components where some components have their own internal functions and data that is not directly accessible by other components of the TSF. This limits the access from a component to the other component on the SPU. |

| P.SW_Crypto-Service     | SW Cryptographic service of the TOE The TOE provides secure software based cryptographic services for the IC Embedded Software. Application Note: the following crypto service is supported by software: TDES.                                                                                           |

## 5.4 Assumptions

The following assumptions are defined in [ICPP].

Table 5-3 Security assumptions

| Assumption       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.Process-Sec-IC | Protection during Packaging, Finishing, and Personalization It is assumed that security procedures are used after delivery of the TOE by the TOE Manufacturer up to delivery to the end-consumer to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft, or unauthorized use).  This means that the Phases after TOE Delivery (refer to Sections 1.2.2 and 7.1 in [ICPP]) are assumed to be protected appropriately. For a preliminary list of assets to be protected, refer to paragraph 96 (page 29 in [ICPP]). |

| A.Resp-Appl      | Treatment of User Data of the Composite TOE  All user data of the Composite TOE are owned by Security IC Embedded  Software. Therefore, it must be assumed that security relevant user data of the  Composite TOE (especially cryptographic keys) are treated by the Security IC  Embedded Software as defined for its specific application context.                                                                                                                                                                                                                                                                 |

## **6** Security objectives

The Security Objectives are taken from [ICPP] with some additional security objectives added.

## **6.1 Security objectives for the TOE**

Table 6-1 Security objectives for the TOE

| Objective           | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O.Leak-Inherent     | Protection against Inherent Information Leakage The TOE must provide protection against disclosure of confidential data stored and/or processed in the Security IC by measurement and analysis of the shape and amplitude of signals (for example on the power, clock, or I/O lines) and by measurement and analysis of the time between events found by measuring signals (for instance, on the power, clock, or I/O lines). |

| O.Phys-Probing      | Protection against Physical Probing (Refined) Refinement: The TOE must provide protection against disclosure/reconstruction of user data while <i>transferred or</i> stored in protected memory areas and processed <i>by the hardware</i> or against the disclosure of other critical information about the operation of the TOE.                                                                                            |

|                     | This includes protection against measuring through galvanic contacts, which is direct physical probing on the chips surface except on pads being bonded (using standard tools for measuring voltage and current) or                                                                                                                                                                                                           |

|                     | measuring not using galvanic contacts but other types of physical interaction between charges (using tools used in solid-state physics research and IC failure analysis) with a prior reverse-engineering to understand the design and its properties and functions.                                                                                                                                                          |

|                     | The TOE must be designed and fabricated so that it requires a high combination of complex equipment, knowledge, skill, and time to derive detailed design information or other information that could be used to compromise security through such a physical attack.                                                                                                                                                          |

| O.Malfunction       | Protection against Malfunctions                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | The TOE must ensure its correct operation.  The TOE must indicate or prevent its operation outside the normal operating conditions where reliability and secure operation have not been proven or tested. This is to prevent malfunctions. Examples of environmental conditions are voltage, clock frequency, temperature, or external energy fields.                                                                         |

| O.Phys-Manipulation | Protection against Physical Manipulation                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | The TOE must provide protection against manipulation of the TOE (including its software and TSF data), the Security IC Embedded Software, and user data of the Composite TOE.                                                                                                                                                                                                                                                 |

|                     | This includes protection against reverse-engineering (understanding the design and its properties and functions), manipulation of the hardware and any data, as well as undetected manipulation of memory contents.                                                                                                                                                                                                           |

| Objective                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O.Leak-Forced            | Protection against Forced Information Leakage  The Security IC must be protected against disclosure of confidential data processed in the Security IC (using methods as described under O.Leak-Inherent) even if the information leakage is not inherent but caused by the attacker by forcing a malfunction (see O.Malfunction: Protection against Malfunctions)  and/or                                                                                                                                                                                              |

|                          | <ul> <li>by a physical manipulation (see O.Phys-Manipulation: Protection against<br/>Physical Manipulation).</li> <li>If this is not the case, signals that normally do not contain significant information<br/>about secrets could become an information channel for a leakage attack.</li> </ul>                                                                                                                                                                                                                                                                     |

| O.Abuse-Func             | Protection against Abuse of Functionality The TOE must prevent that functions of the TOE, which may not be used after TOE Delivery, can be abused to (i) disclose critical user data of the Composite TOE, (ii) manipulate critical user data of the Composite TOE, (iii) manipulate Security IC Embedded Software, or (iv) bypass, deactivate, change, or explore security features or security services of the TOE. Details depend, for instance, on the capabilities of the Test Features provided by the IC Dedicated Test Software, which are not specified here. |

| O.Identification         | TOE Identification The TOE must provide means to store Initialization Data and Prepersonalization Data in its non-volatile memory. The Initialization Data (or parts of it) are used for TOE identification.                                                                                                                                                                                                                                                                                                                                                           |

| O.RND                    | Random Numbers The TOE will ensure the cryptographic quality of random number generation. For instance, random numbers shall not be predictable and shall have a sufficient entropy. The TOE will ensure that no information about the produced random numbers is available to an attacker because they might be used, for instance, to generate cryptographic keys.                                                                                                                                                                                                   |

| O.AES                    | Cryptographic service AES  The TOE provides secure hardware based cryptographic services for the AES for encryption and decryption.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| O.SHA                    | Cryptographic Service Hash Function The TOE provides secure hardware-based cryptographic services for secure hash calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Security Objectives in a | addition to the ones defined in [ICPP]:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |