# Applying the CCV3 ADV Class to Hardware

Wolfgang Killmann T-Systems GEI GmbH

Motivation of the talk

The assurance class Development ADV was changed – significant from CC version 2.3 to CC version 3.0 – to some extent from CC version 3.0 to CC version 3.1

CC and CEM explain the new aspects mainly for software TOE (e.g. ADV\_TDS, ADV\_ARC)

How do we apply the new ADV aspects to hardware?

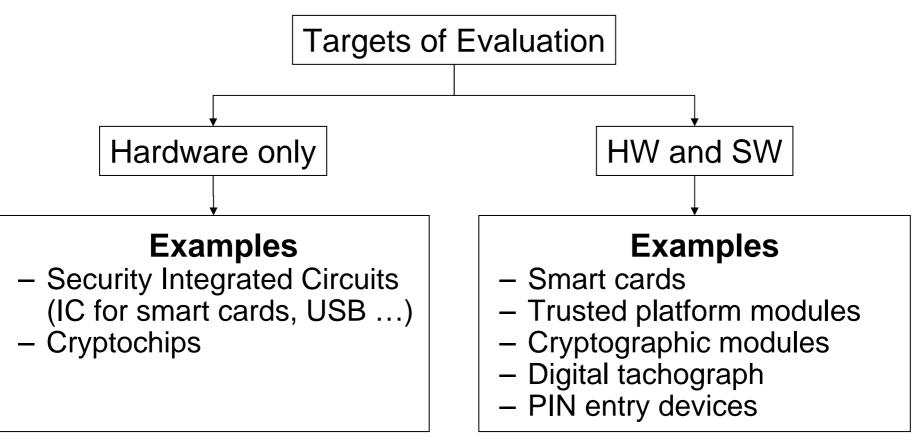

#### Introduction Target of Evaluation including hardware

A real IT system needs HW,

a TOE consists of HW or runs on HW platform or needs an OS running on HW

····**T**···Systems·

Introduction

Security Functional Requirements to Hardware

# Security services provided by hardware

- Cryptographic operation FCS\_COP

- Physical random number generators (FCS\_RNG)

- Time stamps FPT\_STM

# **TSF** protection

- TSF physical protection FPT\_PHP

- TSF self test FPT\_TST

- Fail secure FPT\_FLS, Fault tolerance FRU\_FLT

- Internal TOE (TSF data) transfer FDP\_ITT, FPT\_ITT

# SFR for HW in combination with SW

– Mainly the same but more complex e.g. coprocessor for modular arithmetic  $\rightarrow$  RSA, ECC

Functional Specification ADV\_FSP TSFI and Ports

TSFI - consist of all means for users

- to invoke a service from the TSF (by supplying data that is processed by the TSF) and the corresponding responses to those service invocations or

- (2) to affect the behaviour or the security of the TSF.

- **Port** a physical entry or exit point of the TOE that provides access to the TOE for physical signals, represented by logical interfaces, including power supply.

TOE ports shall be described and examined at least for

- side channel analysis (inherent or forced)

- fault induction analysis (perturbation)

····· **F**··· Syst

Functional Specification ADV\_FSP TOE boundary

**TOE physical boundary** - an explicitly defined continuous perimeter that establishes the physical bounds of the TOE and contains all the hardware, software, and/or firmware components of the TOE.

Physical boundary shall be described and examined for

- physical protection (FPT\_PHP)

- completeness of the port and interface description, including areas of emanation and for irradiation

- consistency of TOE architecture, design, and implementation

TOE Design ADV\_TDS General remark

CC v3 removed CC V2.3 requirements for information about "underlying hardware, firmware, and/or software required by the TSF" and their supporting protection mechanisms

CC v3.1 gives more freedom to define subsystems and modules

# CC v3.1 emphasizes rightly

$\cdots$   $\mathbf{T}$   $\cdots$   $\mathbf{Sv}$

- categorization as SFR-enforcing, SRF-supporting and SFR-non-interfering

- description of **behaviour** and **interaction** of subsystems

- purpose and interfaces of modules

TOE Design ADV\_TDS Algorithmic description

**CC V2.3**: The low-level design shall <u>describe how</u> each TSPenforcing function is provided (ADV\_LLD.2.6C).

**CC V3.0**: For each SFR-enforcing module, the design shall provide an <u>algorithmic description</u> detailed enough to represent the TSF implementation (ADV\_TDS.3.15C).

**CC V3.1**: The design shall describe each SFR-enforcing module in terms of its <u>purpose</u> (ADV\_TDS.3.7C).

TOE design shall describe these modules in terms of

- What does the module do (behaviour)

- How (why) does the module work (purpose) so that determinations can be made about the soundness of the implementation of the SFRs

## TOE Design ADV\_TDS Depth of description

|      |                                                                                          |                              | *                            |                              |                                                                              |                                               |                                               |

|------|------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

|      |                                                                                          | TSF Component                |                              |                              | TSF Module                                                                   |                                               |                                               |

|      |                                                                                          | SFR Enforce                  | SFR Support                  | SFR NI                       | SFR Enforce                                                                  | SFR<br>Support                                | SFR NI                                        |

| EAL4 | ADV_TDS.3<br>Basic modular<br>design (informal<br>presentation)                          | description,<br>interactions | description,<br>interactions | description,<br>interactions | common<br>data,<br>interfaces <sup>(2)</sup> ,<br>algorithmic <sup>(3)</sup> | interaction,<br>purpose                       | interaction,<br>purpose                       |

| EAL5 | ADV_TDS.4<br>Semiformal<br>modular<br>design<br>(semiformal<br>presentation)             | description,<br>interactions | description,<br>interactions | description,<br>interactions | common<br>data,<br>interfaces,<br>algorithmic                                | common<br>data,<br>interfaces,<br>algorithmic | interaction,<br>purpose                       |

| EAL6 | ADV_TDS.5<br>Complete<br>semiformal<br>modular<br>design<br>(semiformal<br>presentation) | description,<br>interactions | description,<br>interactions | description,<br>interactions | common<br>data,<br>interfaces,<br>algorithmic                                | common<br>data,<br>interfaces,<br>algorithmic | common<br>data,<br>interfaces,<br>algorithmic |

<sup>(3)</sup> algorithmic means an algorithmic description of the entire module is provided.

•••••**T**••Systems•

#### **TOE Design ADV\_TDS – Algorithmic Description** Example: Coprocessor for modular arithmetic

- Description of the modular arithmetic coprocessor

→ what modular arithmetic functions are implemented?

- How does the coprocessor work internally?

- $\rightarrow$  registers

- $\rightarrow$  logical operations

- Soundness of the coprocessor design

→ Does the execution time depend on values of the operands?

Example: Arithmetic function

$x \leftarrow x \cdot y \mod n$

Picture: U.S. Patent 5,166,978

•••••**T**••Systems•

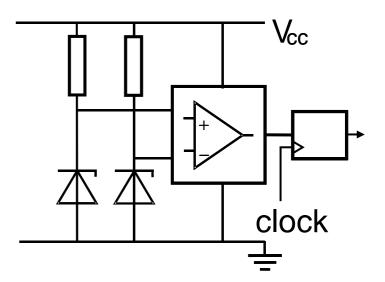

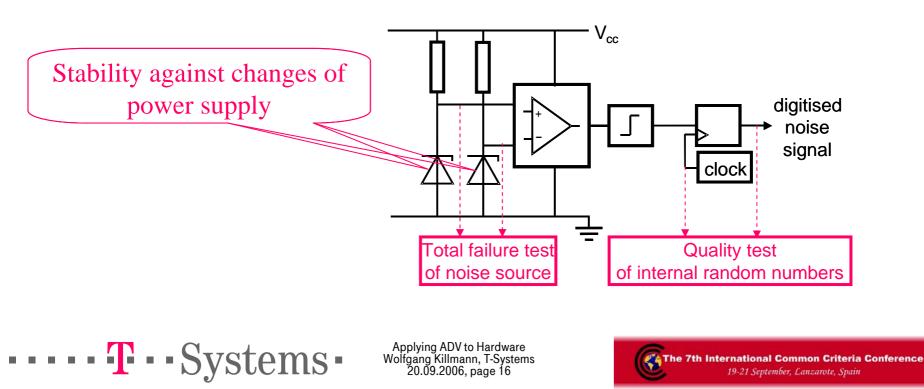

#### **TOE Design ADV\_TDS – Algorithmic Description** Example: Physical Random Number Generator

Applying ADV to Hardware Wolfgang Killmann, T-Systems

20.09.2006. page 11

- Description of the physical random number generator → what are input and output?

- How does the RNG work

- $\rightarrow$  what is the source of randomness?

- $\rightarrow$  why is the source signal random?

- $\rightarrow$  how are the analogous signals digitized to bits?

- Soundness of the RNG design

- $\rightarrow$  What is the entropy of the output bits?

- → Stability of random signal (aging, environmental affected)?

RNG with noise diodes (simplified scheme)

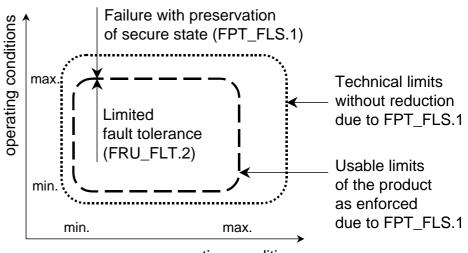

#### TOE Design ADV\_TDS Example: Environmental Control

- Description of environmental control

- $\rightarrow$  detection of violations

- $\rightarrow$  response to violations

- How do the sensors work

→ how does TOE detect

violations of voltage, clock,

temperature, ... (physical

principal of sensors)

→ robustness against light

- Soundness of the design

→ Does the TOE detect the

thresholds outside which

accurate function of the chip

is not ensured

## Example: Security IC PP (BSI-PP-0002)

operating conditions

· · · · · **T** · · Systems ·

TOE Design ADV\_TDS versus ADV\_ARC

All behaviour described in the ADV\_TDS shall be mapped to the TSFIs that invoke it.

$\rightarrow$  TSFI may be implemented by a port but may comprise also the whole physical boundary

Properties of addressed by ADV\_ARC largely have no directly observable interface at the TSF.

$\rightarrow$  criteria to distinguish between ADV\_TDS and ADV\_ARC

For hardware TSF self-protection, domain separation and non-bypassability is enforced by design and mechanisms.

→ analysis of TOE architecture and TOE design is closely related and dependent on each other.

Security Architecture ADV\_ARC General remark

TOE shall enforce the properties of self-protection, domain separation and non-bypassability properties for

- their own hardware TSF and

- their software running on the hardware platform.

Binding of hardware and software is critical to achieve these properties especially in case of composite evaluation, e.g.

- the software relays on hardware TSF like memory management for domain separation,

- the hardware may provide non-bypassability against physical attacks but may support side channel protection only.

Security Architecture ADV\_ARC Secure initialisation process

**TSF initialisation** is directed at the TOE components that are involved in bringing the TSF into an initial secure state (i.e. when all parts of the TSF are operational) when power-on or a reset is applied.

• **1** • • **S**

#### Example:

- power-on self test

- $\rightarrow$  operational mode detection

- $\rightarrow$  check of TOE integrity

- → self-test of Trusted platform module (TPM)

- sleep modes and weak-up procedures

- → sleep mode may disable some TSF (e.g. RNG) but keep other TSF active (e.g. sensors)

Security Architecture ADV\_ARC Self-protection from tampering

"Self-protection" - the ability of the TSF to protect itself from manipulation from external entities that may result in changes to the TSF.

## **Example**: RNG with noise diodes

Security Architecture ADV\_ARC Security domains

#### Security domains -

environments supplied by the TSF for use by potentiallyharmful entities

## Example:

- privileged commands and resources

- $\rightarrow$  CPU protected mode

- → locality of TPM (registers, commands, priority)

- domain separation of memory

→ MMU separates memory

used by trusted OS and

untrusted applications

- power supply for key storage and environmental control independent on main power supply

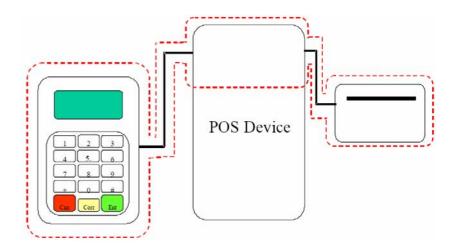

Security Architecture ADV\_ARC Non-bypassability

#### Non-bypassability -

property that the security functionality of the TSF (as specified by the SFRs) is always invoked.

#### Example:

physical tamper response  $\rightarrow$  all over the physical boundary

Source of the Picture: APACS - PIN ENTRY DEVICE – PED GUIDELINE No 11, Type B2 – Individual PIN Pad & IC Reader to POS / EPOS

HW may be managed but can not be changed by SW  $\rightarrow$  "last line of defence"

•••••**T**••Systems•

#### Conclusion

Application of CC version 3 class ADV to hardware requires specific guidance and interpretation for FSP, TDS and ARC

The supporting documents for security integrated circuits shall be updated based on the experience of practical evaluations