# NXP Secure Smart Card Controller N7021 VA Security Target Lite Rev. 2.3 - 2019-06-04 Evaluation documentation

BSI-DSZ-CC-0977

**Evaluation documentation Public**

# **Document Information**

| Info     | Content                                                                                                                                                                                                                                                                           |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | CC, Security Target Lite, N7021 VA                                                                                                                                                                                                                                                |

| Abstract | Security Target Lite of the NXP Secure Smart Card Controller N7021 VA, which is developed and provided by NXP Semiconductors, Business Unit Security & Connectivity according to the Common Criteria for Information Technology Security Evaluation Version 3.1 at EAL6 augmented |

| Rev | Date              | Description                                                                        |

|-----|-------------------|------------------------------------------------------------------------------------|

| 1.0 | 03-April-2017     | First version                                                                      |

| 1.1 | 31-May-2017       | Minor update after certifier feedback.                                             |

| 2.0 | 06-September-2018 | Updated document version numbers in Tab. 1.1. Updated CC conformance to v3.1 rev5. |

| 2.1 | 15-November-2018  | Updated SP 800-67 reference. Updated delivery information in section 1.4.1.1.      |

| 2.2 | 09-May-2019       | Removed single-DES and 2-key TDES references.                                      |

| 2.3 | 06-June-2019      | Updated Guidance and Operation Manual reference.                                   |

# 1 ST Introduction

This chapter is divided into the following sections: "ST Reference", "TOE Reference", "TOE Overview" and "TOE Description".

# 1.1 ST Reference

NXP Secure Smart Card Controller N7021 VA Security Target, 2.3, NXP Semiconductors, 2019-06-04.

# 1.2 TOE Reference

The TOE is named "NXP Secure Smart Card Controller N7021 VA including IC Dedicated Software". In this document the TOE is abbreviated to NXP Secure Smart Card Controller N7021 VA or to N7021 VA. All components of the TOE and their respective version numbers are listed in section 1.4.1.1.

# 1.3 TOE Overview

# 1.3.1 Usage and Major Security Functionality of the TOE

The TOE is the IC hardware platform NXP Secure Smart Card Controller N7021 VA with IC Dedicated Software and documentation describing instruction set and usage of the TOE. The TOE does not include a customer-specific Security IC Embedded Software.

The IC hardware is a microcontroller incorporating a central processing unit (CPU), memories accessible via a Memory Management Unit (MMU), cryptographic coprocessors, other security components and several electrical communication interfaces. The central processing unit supports a 32-/16-bit instruction set optimized for smart card applications. The first and in some cases the second byte of an instruction are used for operation encoding. On-chip memories are ROM, RAM and Flash. The Flash can be used as data or program memory. It consists of highly reliable memory cells, which are designed to provide data integrity. Flash is optimized for applications that require reliable non-volatile data storage for data and program code. Dedicated security functionality protects the contents of all memories. Notice, that the Flash is also referred to as Non-Volatile Memory (NVM) in this Security Target.

The IC Dedicated Software comprises IC Dedicated Test Software for test purposes and IC Dedicated Support Software. The IC Dedicated Support Software consists of the Boot Software, which controls the boot process of the hardware platform. Furthermore, it provides a Firmware Interface and optionally Shared OS Libraries, simplifying access to the hardware for the Security IC Embedded Software. A System Mode OS is available (optional), offering ready-to-use resource and access management for customer applications that do not want to be exposed to the more low-level features of the TOE. The Flashloader OS (optional) supports download of code and data to Flash by the Composite Product Manufacturer before Operational Usage (e.g. during development). The Symmetric Crypto Library (optional) provides simplified access to frequently used symmetric cryptography algorithms.

The documentation includes a Product Data Sheet with several addenda, an Instruction Set Manual, a Guidance and Operation Manual, Symmetric Crypto Library User Manuals and a Wafer and Delivery Specification. This documentation comprises a description of the architecture, the secure configuration and usage of the IC hardware platform and the IC Dedicated Support Software by the Security IC Embedded Software.

The security functionality of the TOE is designed to act as an integral part of a complete security system in order to strengthen the design as a whole. Several security mechanisms are completely implemented in and controlled by the TOE. Other security mechanisms allow for configuration by or even require support of the Security IC Embedded Software.

N7021 VA provides high security for smartcard applications and in particular for being used in the banking and finance market, in electronic commerce or in governmental applications. Hence, N7021 VA shall maintain

- the integrity and the confidentiality of code and data stored in its memories,

- the different TOE modes with the related capabilities for configuration and memory access and

- the integrity, the correct operation and the confidentiality of security functionality provided by the TOE.

This is ensured by the construction of the TOE and its security functionality.

NXP Secure Smart Card Controller N7021 VA basically provides a hardware platform for an implementation of a smart card application with

- functionality to calculate Data Encryption Standard (Triple-DES) with up to three keys,

- hardware to calculate Advanced Encryption Standard (AES) with different key lengths,

- support for large integer arithmetic operations like multiplication, addition and logical operations, which are suitable for public key cryptography and elliptic curve cryptography,

- · a True Random Number Generator.

- · a Hybrid Deterministic Random Number Generator,

- · a Hybrid Physical Random Number Generator,

- · memory management control,

- · cyclic redundancy check (CRC) calculation,

- ISO/IEC 7816 contact interface with UART.

- ISO/IEC14443A contactless interface.

In addition, several security mechanisms are implemented to ensure proper operation as well as integrity and confidentiality of stored data. For example, this includes security mechanisms for memory protection and security exceptions as well as sensors, which allow operation under specified conditions only. Memory encryption is used for memory protection and chip shielding is added to the chip.

**Security Target Lite Public**

Note:

Large integer arithmetic operations are intended to be used for calculation of asymmetric cryptographic algorithms. Any asymmetric cryptographic algorithm utilizing the support for large integer arithmetic operations has to be implemented in the Security IC Embedded Software. The support for large integer arithmetic operations does not provide security functionality like cryptography. The Security IC Embedded Software that implements an asymmetric cryptographic algorithm is not included in this Security Target, but the support for large integer arithmetic operations is a security relevant component of the TOE, which resists to the attacks mentioned in this Security Target and operates correctly as specified in the data sheet. The same scope is applied to the CRC calculation. Similarly, even though single DES and two-key version of TDES are supported, they are not within the scope of evaluation.

### 1.3.2 TOE Type

The TOE NXP Secure Smart Card Controller N7021 VA is provided as IC hardware platform with IC Dedicated Software for various operating systems and applications with high security requirements.

### 1.3.3 Required non-TOE Hardware/Software/Firmware

None

### **TOE Description** 1.4

# **Physical Scope of TOE**

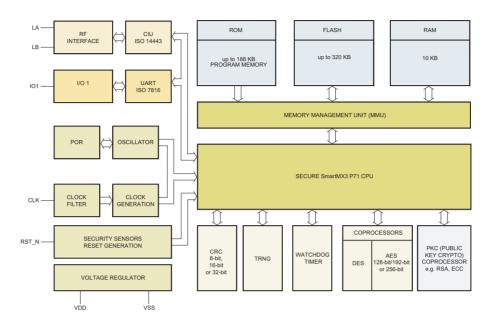

N7021 VA is manufactured in 90nm CMOS technology. A block diagram of the IC hardware is depicted in Figure 1.1.

Fig. 1.1: Block Diagram

N7021 VA consists of the IC hardware and IC Dedicated Software. The IC Dedicated Software is composed of IC Dedicated Test Software for test purposes and IC Dedicated Support Software. The IC Dedicated Test Software contains the Test Software, the IC Dedicated Support Software is composed of the Boot Software, the Firmware Interface, the Shared OS Libraries, the Symmetric Crypto Library, the System Mode OS and the Flashloader OS. All other software is called Security IC Embedded Software. The Security IC Embedded Software is not part of the TOE. All components of the TOE are listed in section 1.4.1.1.

# 1.4.1.1 TOE components

| Type All configurations       | Name                                                   | Version | Form of Delivery           |

|-------------------------------|--------------------------------------------------------|---------|----------------------------|

| IC Hardware                   | N7021                                                  | VA      | Wafer, modules and package |

| IC Dedicated Test<br>Software | Test Software                                          | 20.0    | On-chip software           |

| IC Dedicated Support          | Boot Software                                          | 20.0    | On-chip software           |

| Software                      | Firmware Interface                                     | 20.0    | On-chip software           |

| Document                      | SmartMX3 family P71D320 Overview, pinning and electri- | 3.1     | PDF via NXP Doc-           |

|                               | cal characteristics, Product Data Sheet [25]           |         | Store                      |

| Document                      | SmartMX3 N7021 Instruction Set Manual, Product Data    | 1.4     | PDF via NXP Doc-           |

|                               | Sheet addendum [16]                                    |         | Store                      |

| Туре                             | Name                                                                                                                     | Version | Form of Delivery                  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|

| Document                         | SmartMX3 family N7021 Wafer and delivery specification,<br>Data Sheet addendum [24]                                      | 1.3     | PDF via NXP Doc-<br>Store         |

| Document                         | SmartMX3 N7021 Post Delivery Configuration Post Deliv-                                                                   | 1.1     | PDF via NXP Doc-                  |

|                                  | ery Configuration, Data Sheet addendum [21]                                                                              |         | Store                             |

| Document                         | SmartMX3 N7021 Chip Health Mode, Data Sheet addendum [14]                                                                | 1.0     | PDF via NXP Doc-<br>Store         |

| Document                         | SmartMX3 N7021 Peripheral Configuration and Use, Data Sheet addendum [20]                                                | 1.4     | PDF via NXP Doc-<br>Store         |

| Document                         | SmartMX3 N7021 MMU configuration & FW interface, Data Sheet addendum [18]                                                | 1.5     | PDF via NXP Doc-<br>Store         |

| Document                         | SmartMX3 N7021 Inter-Card Communication, Data Sheet addendum [17]                                                        | 1.1     | PDF via NXP Doc-<br>Store         |

| Document                         | SmartMX3 N7021 NVM Operate Function, Data Sheet addendum [19]                                                            | 1.0     | PDF via NXP Doc-<br>Store         |

| Document                         | NXP Secure Smart Card Controller N7021 Information on<br>Guidance and Operation, Guidance and Operation Man-<br>ual [13] | 1.4     | PDF via NXP Doc-<br>Store         |

| Deliverables of the Flas         | shloader OS                                                                                                              |         |                                   |

| IC Dedicated Support<br>Software | Flashloader OS                                                                                                           | 20.0    | On-chip software                  |

| Document                         | SmartMX3 N7021 FlashLoader, Product Data Sheet addendum [15]                                                             | 1.3     | PDF via NXP Doc-<br>Store         |

| Deliverables of the Sha          | ared OS Libraries                                                                                                        |         |                                   |

| IC Dedicated Support<br>Software | Shared OS Libraries                                                                                                      | 20.0    | On-chip software                  |

| Library File                     | libComm                                                                                                                  |         | SDK installer via NXP<br>DocStore |

| Library File                     | libCrc                                                                                                                   |         | SDK installer via NXP<br>DocStore |

| Library File                     | libMem                                                                                                                   |         | SDK installer via NXP<br>DocStore |

| Library File                     | libFL                                                                                                                    |         | SDK installer via NXP<br>DocStore |

| Document                         | SmartMX3 N7021 Shared OS libraries, Data Sheet addendum [22]                                                             | 1.2     | PDF via NXP Doc-<br>Store         |

| Deliverables of the Sys          | stem Mode OS                                                                                                             |         |                                   |

| IC Dedicated Support<br>Software | System Mode OS                                                                                                           | 20.0    | On-chip software                  |

| Туре                             | Name                                                                                                      | Version                                      | Form of Delivery                  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|

| Document                         | SmartMX3 N7021 NXP System Mode OS Interface, Data Sheet addendum [23]                                     | nterface, Data 1.6 PDF via NXP Doc-<br>Store |                                   |

| Deliverables of the Syr          | mmetric Crypto Library                                                                                    |                                              |                                   |

| IC Dedicated Support<br>Software | Crypto Library Iron                                                                                       | 2.0.6-01                                     | On-chip software                  |

| Library Files                    | Crypto Library Iron                                                                                       | 2.0.6-01                                     | SDK installer via NXP<br>DocStore |

| Document                         | Crypto Library V1.0 on N7021 VA, Symmetric Cipher Library (SymCfg), User manual [28]                      | 1.2                                          | PDF via NXP Doc-<br>Store         |

| Document                         | N7021 Crypto Library, RNG Library, User manual [27]                                                       | 1.3                                          | PDF via NXP Doc-<br>Store         |

| Document                         | N7021 Crypto Library, Utils Library, User manual [29]                                                     | 1.1                                          | PDF via NXP Doc-<br>Store         |

| Document                         | Crypto Library Iron on N7021 VA, Information on Guidance and Operation, Guidance and Operation Manual [7] | 2.0                                          | PDF via NXP Doc-<br>Store         |

Tab. 1.1: Components of the TOE

The IC Hardware is delivered to the customer by secure transport in parcels sealed with special tape. The customer can examine the tape sealing to make sure that the TOE has not been manipulated during transport. The documentation can be downloaded by the customer from the NXP DocStore website after registration. Library files (object files, header files and linker scripts) are also made available to the customer via NXP DocStore, as part of a downloadable and installable SDK.

The logical dependencies of the TOE components are given in Section 1.4.3.2.

The IC Hardware is identified by a nameplate that is located in the layout of the chip (see [24] how to inspect the nameplate). The IC Dedicated Software is identified by 'IC Dedicated Software version', which can be read out by the Security IC Embedded Software via a GetVersion command as described in [14].

# **Evaluated Configurations**

The N7021 VA can be delivered with various configuration options as described in this section. The configuration options are divided into two groups: major configuration options according to section 1.4.2.1 and minor configuration options according to section 1.4.2.2.

# 1.4.2.1 Major configuration options

Three major configurations can be chosen by the customer during the ordering process:

- · Configuration based on 320 kBytes of Flash memory as code space

- · Configuration based on 240 kBytes of Flash memory as code space

- · Configuration based on 144 kBytes of ROM memory as code space

Each major configuration is provided with several minor configuration options, which are introduced in Section 1.4.2.2. Each major configuration also provides customers with several options for reconfiguration (Post Delivery Configuration), which are described in Section 1.4.2.3 in detail.

# 1.4.2.2 Minor configuration options

Minor configurations are chosen by the customer during the ordering process as detailed in Table 1.2.

| Product option          | Choices                           | Description                                                       |

|-------------------------|-----------------------------------|-------------------------------------------------------------------|

| Customer Type           | System Mode Customer, User        | Select the hierarchical interaction model of the Security IC      |

|                         | Mode Customer                     | Embedded Software.                                                |

| Use Flash Loader        | Yes, No                           | If selected, allow the download of an arbitrary card image into   |

|                         |                                   | logical card B using the Flashloader.                             |

| UID Option              | <b>7B UID</b> , 4B FNUID, 10B UID | Determines the UID setting.                                       |

| Enable Contactless      | Enabled, Disabled                 | If enabled, the contactless interface is activated in the product |

| Interface               |                                   | configuration.                                                    |

| Input Capacitance       | <b>17pF</b> , 56pF, 70pF          | Nominal input capacitance for ISO/IEC 14443 contactless in-       |

|                         |                                   | terface.                                                          |

| Data Rate               | AII, 106kbps, 106-848kbps, 106-   | Set the available data rates.                                     |

|                         | 848kbps and VHBR rates up to      |                                                                   |

|                         | 3.2Mbps                           |                                                                   |

| Enable Contact In-      | Enabled, Disabled                 | If enabled, the contact interface is activated in the product     |

| terface                 |                                   | configuration.                                                    |

| PUF option              | Enabled, Disabled                 | If enabled, the device supports the PUF security functionality.   |

| MIFARE DESFire          | <b>Disabled</b> , 2K, 4K, 8K, 32K | Configure the available MIFARE DESFire image in logical           |

| EV2 Option <sup>1</sup> |                                   | card A of the system <sup>1</sup> .                               |

| MIFARE Plus EV1         | Disabled, 2K, 4K                  | Configure the available MIFARE PLUS2 image in logical card        |

| Option <sup>1</sup>     |                                   | A of the system <sup>1</sup> .                                    |

| Enable Chip Health      | Enabled, Disabled                 | Enable the availability of Chip Health Mode (CHM).                |

| Mode                    |                                   |                                                                   |

Tab. 1.2: Evaluated minor configuration options

Regardless of the minor configuration options selected, the TOE will always remain in a certified configuration.

# 1.4.2.3 Post Delivery Configuration

Post Delivery Configuration (PDC) can be used by the customer after the TOE has been delivered by NXP. These options can be used to tailor the TOE to specific customer requirements. The Post Delivery Configuration settings can be changed multiple times but must be set permanently by the customer before the TOE is delivered to phase 7 of the life-cycle.

<sup>&</sup>lt;sup>1</sup>MIFARE emulations are not part of the TSF and are therefore not in scope of this certification.

Table 1.3 lists those configuration parameters that can be set by PDC in the NXP Secure Smart Card Controller N7021 VA.

| PDC option                                                              | Description                                                                                                                                                                   |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total requested Flash size                                              | Define the total number of customer available Flash pages. PDC can only reduce this value.                                                                                    |

| Contact/contactless/dual operation mode                                 | Define the operation mode which can be either "contact only", "contactless only", or "dual". Interfaces can only be deactivated by PDC if they were selected during ordering. |

| Disable cryptographic functions                                         | Define the available cryptographic options. Each of the three functions (DES AES, PKCC) can be independently disabled.                                                        |

| Outside Anti-Wear partition size Card B                                 | Defines the outside anti-wear partition flash size available for logical card B.                                                                                              |

| Inside Anti-Wear partition size Card<br>B and Free Page Pool (FPP) size | Defines the inside anti-wear partition flash page size of logical card B and the number of additional Free Page Pool pages. Wear-levelling increases Flash endurance.         |

| Default logical card                                                    | Define which logical card SM (A or B) should be launched after finishing the boot sequence.                                                                                   |

| Default OS                                                              | Define which operating system (either OS 1 or OS 2) should be launched after finishing the boot sequence of the selected logical card.                                        |

| Card A/Card B RAM partition split                                       | Define how the RAM is split between Card A and Card B.                                                                                                                        |

| Basic control setting and codebase for OS1 in Card B                    | Set the codebase (memory offset) and options for OS1 in Card B.                                                                                                               |

| Basic control setting and codebase for OS2 in Card B                    | Set the codebase (memory offset) and options for OS2 in Card B.                                                                                                               |

Tab. 1.3: Post Delivery Configuration

As indicated in the description of the PDC options, they can only be used to downgrade some configurations, it is not possible to enable functionality. The Post Delivery Configuration can be accessed using chip health mode functionality in combination with the ISO/IEC 7816 contact interface. PDC configures the availability of TSF. Deactivating TSF is identical to not utilizing the functionality and therefore the TOE will remain in a certified configuration. For further details regarding PDC refer to [21].

# 1.4.2.4 Dependencies on minor configuration and PDC

Depending on the minor configuration options chosen during the ordering process, and on the changes made using PDC, some of the security functionality mentioned in this ST is no longer available. Table 1.4 below lists these dependencies.

| Option           | Feature   | SFRs comment                                                         |

|------------------|-----------|----------------------------------------------------------------------|

| Use Flash Loader | SS.Loader | SFRs are still in place to ensure correct blocking of functionality. |

| Option           | Feature     | SFRs comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip Health Mode | SS.RECONFIG | Feature CHM is not available, SS.RECONFIG itself is still available. PDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |             | also available via System Mode API.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Disable DES      | SS.HW_TDES, | Related SFRs are deactivated. (SF.Object_Reuse is still available)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | SS.SW_DES   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Disable AES      | SS.HW_AES,  | Related SFRs are deactivated. AES functionality is mandatory for SF.PUF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  | SS.SW_AES,  | SS.RECONFIG needs AES for PDC configuration and CHM authentication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  | SF.PUF,     | (SF.Object_Reuse is still available)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | SS.RECONFIG |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PUF option       | SF.PUF      | Related SFRs are deactivated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |             | The same of the sa |

Tab. 1.4: Dependencies on minor configuration and PDC

# 1.4.2.5 Evaluated package types

The commercial types are named according to the format *P7nxeeeypp(p)/mvrrff(o)*.

The characters in the above format are coded as described in Table 1.5 and Table 1.6. The commercial type name is composed of fixed symbols, which are detailed in Table 1.5, and variable entries, which are filled in according to the rules in Table 1.6.

| Variable | Description                                                       | Values                  | <b>Evaluated Options</b>                                                                                                                 |

|----------|-------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| n        | indicates ROM or Flash product                                    | numeric                 | '0' for ROM, '1' for Flash                                                                                                               |

| X        | Interface and Feature Configuration                               | alpha numeric           | 'D' for Dual Interface                                                                                                                   |

| eee      | Indication of Flash or ROM Size, depending on variable $n$        | alpha numeric           |                                                                                                                                          |

| у        | MIFARE Emulation Option Configuration                             | alphanumeric            | 'P' for no MIFARE emulation,<br>'D' for DESFire EV2, 'M' for<br>MIFARE Plus EV1                                                          |

| pp(p)    | Package delivery type                                             | alpha numeric           | see table 1.6                                                                                                                            |

| /        | separator (mandatory)                                             |                         |                                                                                                                                          |

| m        | Manufacturer identifier                                           | alpha numeric           | '9' for TSMC                                                                                                                             |

| V        | Version of mask set                                               | alphabetic              | 'A' for HW version VA                                                                                                                    |

| rr       | NCN number, which identifies the NXP content at TOE delivery      | alpha numeric           | specific to a certain combi-<br>nation of major and minor<br>options and IC Dedicated<br>Software version and other<br>NXP data elements |

| ff       | CCN number, which identifies the customer content at TOE delivery | alpha numeric           | specific to customer identity<br>and content of code and data<br>to be uploaded on behalf of<br>the customer                             |

| (o)      | Option                                                            | alpha numeric, optional |                                                                                                                                          |

| Variable Description Values Evaluated Options |

|-----------------------------------------------|

|-----------------------------------------------|

Tab. 1.5: Variable Definitions for Commercial Type Names

| Type | Description                                                                                                                                                                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unn  | Wafer not thinner than $50\mu m$ . The numbers "nn" in "Unn" identify a specific wafer delivery type (thickness, manufacturing process and packing option)                                                                                                                               |

| Xnn  | Chip card module. The numbers "nn" in "Xnn" identify a specific chip module delivery type (module type, manufacturing process and packing option)                                                                                                                                        |

| An   | Contactless chip card module or inlay type (assembly containing the TOE and a contactless antenna on a carrier material. The "n" in "An" identifies a specific contactless module or inlay delivery type (type of contactless module or inlay, manufacturing process and packing option) |

Tab. 1.6: Supported Package Types

Security during development and production is ensured for all package types listed above, for details refer to section 1.4.4.

The commercial type name identifies major configuration and package type of the TOE as well as the Security IC Embedded Software. However, the commercial type name does not itemize the minor configuration options of the TOE, which are introduced in section 1.4.2.2. Instead, minor configuration options are identified during the ordering process, which is coupled to the NCN and CCN of the commercial type name.

### 1.4.3 Logical Scope of TOE

# 1.4.3.1 Hardware Description

The TOE distinguishes five TOE modes:

- 1. Super System Mode (SSM)

- 2. Configuration Mode (CM)

- 3. Test Mode (Test Mode)

- 4. System Mode (SM)

- 5. User Mode (UM)

The Super System Mode is not available to the Security IC Embedded Software. In Super System Mode the TOE executes the Boot Software resp. the IC Dedicated Test Software. Notice that the Firmware Interface also executes in Super System Mode and other parts are executed in System Mode and can be accessed via socalled system calls either from User Mode or System Mode. The Security IC Embedded Software may execute in System Mode or User Mode. Note also that the CPU itself only distinguishes between the User Mode, the System Mode and the Super System Mode. From CPU's perspective there is no difference between the Test Mode, the

Configuration Mode and the Super System Mode. The difference from system perspective is only that the Test Mode and Configuration Mode can extend their access rights to Special Function Registers compared to what is visible in Super System Mode (it can grant access to test features). However, this is enforced by the Memory Management Unit where the Test Mode and Configuration Mode are modelled as an own mode that has extended access rights compared to Super System Mode.

The N7021 VA is able to control two different logical phases. After production of the Security IC every start-up or reset completes with execution of the IC Dedicated Test Software. The test functionality is disabled at the end of the production test. Afterwards, every start-up or reset ends up in System Mode or User Mode, depending on the minor configuration 'Customer Type' selected by the customer.

System Mode and User Mode are available to the developer of the Security IC Embedded Software. System Mode has broader access to the hardware components available to the Security IC Embedded Software. User Mode has restricted access to the CPU, specific Special Function Registers and the memories depending on the access rights granted by software running in System Mode. The hardware components are controlled by the Security IC Embedded Software via Special Function Registers. Both are interrelated to the activities of the CPU, the Memory Management Unit, interrupt control, I/O configuration, NVM, timers and the coprocessors.

The N7021 VA provides interrupts. Interrupts force a jump to a specific fixed vector address in the ROM or Flash. Any interrupt can therefore be controlled and guided by a specific part of the Security IC Embedded Software. In addition, N7021 VA provides user calls and system calls. These calls have to be explicitly done by the Security IC Embedded Software via dedicated CPU instructions. A user call starts the execution of related code dedicated to one lower privileged mode (Super System Mode to System Mode or System Mode to User Mode). A system call starts the execution of related code dedicated to one higher privileged mode (User Mode to System Mode or System Mode to System Mode).

The Watchdog timer is intended to abort irregular program executions by a time-out mechanism and is enabled and configured by the Security IC Embedded Software.

The N7021 VA incorporates 320 kBytes of Flash, 10 kBytes of RAM and up to 188 kBytes of program memory available in ROM. Access control to all three memory types is enforced by a Memory Management Unit (MMU). The System Mode OS provides a simplification of the resource management (e.g. MMU firewall settings, dynamic segment setup, peripheral access control). The MMU partitions each memory into several parts, defined as objects in the Hardware Access Control Policy (see section 6.1.6).

The Triple-DES coprocessor supports single DES and Triple-DES operations. Only Triple-DES in 3-key operation (168-bit) is in the scope of this evaluation. The AES coprocessor supports AES operation with three different key lengths of 128, 192 or 256 bit. The Public Key Crypto Coprocessor (PKCC) coprocessor supplies basic arithmetic functions to support implementation of asymmetric cryptographic algorithms by the Security IC Embedded Software. The random number generator provides true random numbers without pseudo random calculation. The deterministic random number generator provides pseudo-random calculation seeded by the true random number generator. The CRC coprocessor provides CRC generation polynomial CRC-8, CRC-16 and CRC-32.

The N7021 VA operates with a single external power supply of 1.8V, 3V or 5V nominal. Alternatively the TOE can be supplied via the RF interface by means of inductive coupling. The maximum external clock frequency used

for synchronization of the ISO/IEC 7816 communication is 10 MHz nominal, the CPU and all coprocessors are supplied exclusively with an internally generated clock signal which frequency can be selected by the Security IC Embedded Software. The N7021 VA provides power saving modes with reduced activity. These are named IDLE Mode and SLEEP Mode, of which the latter one includes CLOCK STOP Mode.

The TOE protects secret data, which are stored to and operated by the TOE, against physical tampering. A memory encryption is added to the memories RAM, ROM and Flash such that data stored to these memories is encrypted. Chip shielding is added in form of active and passive shield over the whole chip surface. Sensors in form of light, voltage, temperature and frequency sensors are distributed over the chip area. The security functionality of the IC hardware platform is mainly provided by the TOE, and completed by the Security IC Embedded Software. This causes dependencies between the security functionality of the TOE and the security functionality provided by the Security IC Embedded Software.

# 1.4.3.2 Software Description

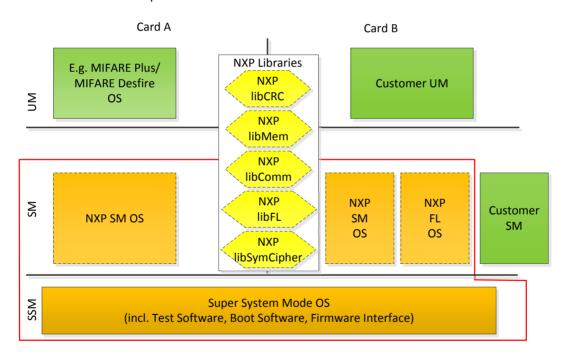

Figure 1.2 illustrates the different pieces of software available on the TOE.

Fig. 1.2: Software Components of the TOE

The N7021 VA supports two logical cards (Card A and Card B). Both logical cards are divided into a User Mode and a System Mode. The logical location of the Security IC Embedded Software, depends on the usage of the IC hardware platform. Card A is reserved for Security IC Embedded Software developed by NXP (for example, a MIFARE Operating System). This code is stored in the UM-A Code Seg (which is the User Mode of Card A). Card B is available for Security IC Embedded Software developed by the customer, which can be stored in

either UM-B\_Code\_Seg (User Mode of Card B) or stored in the SM-B\_Code\_Seg (System Mode of Card B) if the customer is a System Mode customer. If a customer did not order any NXP developed Security IC Embedded Software product (such as MIFARE), then User Mode Card A is not present. The physical location of the Security IC Embedded Software can be either in ROM or in Flash and is not in the scope of this evaluation.

The separation between two logical cards (Card A and Card B) is provided by the so-called "Vertical IP firewall" which allows having two completely separated logical cards on the same hardware without any unintended impact on each other. Because a logical card is also divided into a User Mode and a System Mode, it is possible to implement a security feature called "Secure User Mode Box".

The "Secure User Mode Box" makes sure that NXP code and data residing in the User Mode of Card A (for example, a MIFARE Operating System) cannot have any security impact on the certified IC configuration. This is achieved because the System Mode OS in logical Card A restricts access of code executed in User Mode on logical Card A such that no influence to any other mode and card is possible. For the "Secure User Mode Box" fixed values are NXP defined during production.

Using shared memory segments it is possible to share data or code between the separated logical cards. The owner of a memory block has to explicitly allow this kind of sharing. The libraries are shared between the logical cards using this mechanism, reducing the footprint, as code only has to be present on the device once. An Intercard communication mechanism allows the currently active card to send a message to the inactive card with a request for card switching. This mechanism allows for the handover of execution between the logical cards.

The IC Dedicated Test Software is developed by NXP and embedded in the Test Software. The IC Dedicated Test Software includes the test operating system, test routines for the various blocks of the circuitry, control flags for the status of the Flash's manufacturer area and shutdown functions to ensure that security relevant test routines cannot be executed illegally after phase 3. This is stored in the SSM\_Data\_Seg. Moreover, the IC Dedicated Test Software is used to download patch code related to System Mode (stored in SM-A\_Code\_Seg or SM-B Code Seg) or User Mode (stored in UM-A Code Seg or UM-B Code Seg).

The IC Dedicated Support Software comprises the following parts:

- The Boot Software is executed after each reset of the TOE, i.e. every time when the TOE starts. It sets up the

TOE and does some basic configuration of the hardware based on the settings stored in SSM\_Data\_Seg,

respectively. The Boot Software is stored in the SSM\_Code\_Seg.

- The Firmware Interface is stored in the SSM\_Code\_Seg. It provides low-level flash management, the Post

Delivery Configuration feature and basic system functionality like self-testing, error-counter handling and

reset functionality. Notice, that Boot Software and IC Dedicated Test Software also access the Firmware

Interface.

- 3. The System Mode OS is an Operating System developed by NXP and stored in the SM-A\_Code\_Seg and/or in the SM-B\_Code\_Seg and is accessed by the Security IC Embedded Software via system calls. It offers ready-to-use resource and access management for arbitrary customer applications that do not want to be exposed to the more low-level features such as MMU configuration. The System Mode OS on Card A is

mandatory when the Flashloader OS is part of the product, when library code is shared between the logical cards or when Card A is activated. The System Mode OS on Card B is mandatory for User Mode customers. For System Mode customers who do not need any NXP library and no Flashloader OS and no activated Card A, the System Mode OS is deactivated and cannot be executed.

- 4. The Shared OS Libraries are an optional module and can be stored in any Card and mode. It provides simplified communication, CRC and memory functions to the Security IC Embedded Software. The Shared OS Libraries are required by the Flashloader OS.

- 5. The Symmetric Crypto Library is an optional library which provides functions to access AES, DES, RNG and Secure Operations functionality to the Security IC Embedded Software. It is mandatory for the Flashloader OS. The physical location of the Symmetric Crypto Library depends on the configuration selected by the customer. For products that include the Flashloader OS, the Symmetric Crypto Library is located in ROM. For products without the Flashloader OS, the physical location depends on how the customer linked the Symmetric Crypto Library into their Security IC Embedded Software using the development tools.

- 6. The Flashloader OS is an optional module and stored in the SM-B Code Seg and cannot be directly accessed by the Security IC Embedded Software. It supports the download of code and data to Flash by the Composite Product Manufacturer before Operational Usage (e.g. during development). This functionality can be made unavailable after usage. When the Flashloader OS module is available, the Shared OS Libraries, Symmetric Crypto Library and System Mode OS become mandatory.

All logical dependencies of the IC Dedicated Support Software are described in the definitions above.

### 1.4.3.3 Security functionality dependency on optional software

As some of the modules and libraries are optional, the security functionality mentioned in this ST also becomes optional. If the Symmetric Crypto Library is not part of the TOE, the SFRs related to SS.SW DES, SS.SW AES, SS.SW\_RNG and SF.Object\_Reuse are not available. If the System Mode OS is optional, SS.Loader will no longer work (as System Mode OS functionally supports SS.Loader). SF.MEM SUB will also not be available, as the System Mode OS makes sure that the MMU gets properly configured for this functionality.

# 1.4.3.4 Documentation

The documents containing a functional description and guidelines for the use of the security functionality, as needed to develop Security IC Embedded Software, are listed in Table 1.1. The whole documentation shall be used by the developer to develop the Security IC Embedded Software.

# Security during Development and Production

The Security IC product life-cycle is scheduled in phases as introduced in the PP [26]. IC Development as well as IC Manufacturing and Testing, which are phases 2 and 3 of the life-cycle, are part of the evaluation. Phase 4 the IC Packaging is also part of the evaluation. The Security IC is delivered at the end of phase 3 or phase 4 in the life-cycle. The development and production environment of the TOE ranges from phase 2 to TOE Delivery.

With respect to Application Note 3 in [26] the TOE supports the authentic delivery using the FabKey feature. For further details refer to the data sheet [25] and the guidance and operation manual [13].

During the design and the layout process only personnel involved in the specific development project for an IC have access to sensitive data. Different teams are responsible for the design data and for customer related data. The production of the wafers includes two different steps regarding the production flow. In the first step the wafers are produced with the fixed masks independent of the NCN or CCN. After that step the wafers are completed with the product type specific data, including ROM and Flash Code, and data (if applicable) as identified by NCN and CCN. The test process of every die is performed by a test center of NXP. Delivery processes between the involved sites provide accountability and traceability of the TOE. NXP embeds the dice into modules, inlays or packages depending on the individual commercial type.

Information about non-functional items (so-called failed die) is stored on electronic media, and the access to this media made available with the delivery. The availability of major configuration options of the TOE in package types is detailed in section 1.4.2.1.

# 1.4.5 TOE Intended Usage

The end-consumer environment of the TOE is phase 7 of the Security IC product life-cycle as defined in the PP [26]. In this phase the Security IC product is in usage by the end-consumer. Its method of use now depends on the Security IC Embedded Software. The Security ICs including the N7021 VA can be used to perform various functions in a wide range of applications. Examples are identity cards, Banking Cards, Pay-TV, Health cards and Transportation cards. The end-user environment covers a wide spectrum of very different functions, thus making it difficult to monitor and avoid abuse of the TOE. The TOE is intended to be used in an insecure environment, which does not protect against threats.

The device is developed for high-end safeguarded applications, and is designed for embedding into chip cards according to ISO/IEC 7816 [9] and for contactless applications according to ISO/IEC 14443 [30]. Usually a Security IC (e.g. a smartcard) is assigned to a single individual only, but it may also be used by multiple applications in a multi-provider environment. Therefore the TOE might store and process secrets of several systems, which must be protected from each other. The TOE then must meet security requirements for each single security module. Secret data shall be used as input for calculation of authentication data, calculation of signatures and encryption of data and keys.

In development and production environment of the TOE the Security IC Embedded Software developer and system integrators such as the terminal software developer may use samples of the TOE for their testing purposes. It is not intended that they are able to change the behaviour of the Security IC in another way than an end-consumer. The user environment of the TOE ranges from TOE delivery to phase 7 of the Security IC product life-cycle, and must be a controlled environment up to phase 6.

Note:

The phases from TOE Delivery to phase 7 of the Security IC Product life-cycle are not part of the TOE construction process in the sense of this Security Target. Information about these phases is just included to describe how the TOE is used after its construction. Nevertheless such security functionality of the

TOE, that is independent of the Security IC Embedded Software, is active at TOE Delivery and cannot be disabled by the Security IC Embedded Software in the following phases.

### 1.4.6 Interface of the TOE

The electrical interface of the N7021 VA are the pads to connect the lines power supply, ground, reset input, clock input, serial communication pad I/O1, as well as two pads (called LA and LB) for the antenna of the RF interface (See Figure 1.1). Communication with the TOE can be established via the contact interface through the ISO/IEC 7816 UART or direct usage of the I/O ports. Contactless communication is done via the the contactless interface unit (CIU) compatible to ISO/IEC 14443.

The logical interface of the TOE depends on the CPU mode and the associated software.

- Upon every start-up the Boot Software is executed in Super System Mode. This software initializes and configures the TOE. This comprises the selection of IC Dedicated Test Software (before TOE delivery) and of Security IC Embedded Software (after TOE delivery). Only in case the minor configuration option 'Enable Chip Health Mode' is enabled, starting of built-in self test routines and read-out of TOE identification items is supported. If this minor configuration option is disabled the Boot Software provides no interface. In this case there is no possibility to interact with this software. The Boot Software is stored in the SSM Code Seq.

- Before TOE delivery the logical interface is defined by the IC Dedicated Test Software. This IC Dedicated Test Software is executed in Super System Mode and comprises the test operating system used for production testing. IC Dedicated Test Software is embedded in the Test Software.

- In System Mode and User Mode (after TOE Delivery) the software interface is the set of instructions, the bits in the special function registers that are related to these modes and the physical address map of the CPU including memories. The access to the special function registers as well as to the memories depends on the TOE mode configured by the Security IC Embedded Software.

Note:

The logical interface of the TOE that is visible on the electrical interface after TOE Delivery is based on the Security IC Embedded Software developed by the software developer. The identification and authentication of the user in System Mode or User Mode must be controlled by the Security IC Embedded Software.

The chip surface can be seen as an interface of the TOE, too. This interface must be taken into account regarding environmental stress e.g. like temperature and in the case of an attack, for which the attacker manipulates the chip surface.

Note:

An external voltage and timing supply as well as a logical interface are necessary for the operation of the TOE. Beyond the physical behavior the logical interface is defined by the Security IC Embedded Software.

# 2 Conformance Claims

This Security Target claims to be conformant to the Common Criteria version 3.1:

- Common Criteria for Information Technology Security Evaluation, Part 1 Introduction and general model -Version 3.1 CCMB-2017-04-001, Revision 5, April 2017, [3]

- Common Criteria for Information Technology Security Evaluation, Part 2 Security functional components, Version 3.1 CCMB-2017-04-002, Revision 5, April 2017, [4]

- Common Criteria for Information Technology Security Evaluation, Part 3 Security Assurance Components,

Version 3.1 CCMB-2017-04-003, Revision 5, April 2017, [5]

For the evaluation the following methodology will be used:

Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1 CCMB-2017-04-004, Revision 5, April 2017, [6]

This Security Target claims to be CC Part 2 extended and CC Part 3 conformant. The extended Security Functional Requirements are defined in chapter 5.

# 2.1 Package Claim

This Security Target claims conformance to the assurance package **EAL6 augmented**. The augmentations to EAL6 is ALC\_FLR.1. In addition, the Security Target is augmented using the component ASE\_TSS.2, which is chosen to include architectural information on the security functionality of the TOE.

Note:

The Protection Profile (PP) "Security IC Platform Protection Profile with Augmentation Packages" [26] to which this Security Target claims conformance (refer to section 2.2) requires assurance level EAL4 augmented. The changes, which are needed for EAL6, are described in the relevant sections of this Security Target.

The level of evaluation and the functionality of the TOE are chosen in order to allow the confirmation that the TOE is suitable for use within devices compliant with the German Digital Signature Law.

# 2.2 PP Claim