# Security Target for KB100 SCR eSIG

| Zertifizierung | ID:             | BSI-DSZ-CC-1046                     |

|----------------|-----------------|-------------------------------------|

| Document       | ID:             | ASE_KB100SCReSIG                    |

|                | Version:        | 1.10                                |

|                | Status:         | Final                               |

|                | Date:           | 16.02.2018                          |

|                |                 |                                     |

|                | Prepared by:    | Jürgen Meier, Ales Diessner         |

|                | Date/Signature: | 16.02.2018                          |

|                | Checked by:     | Dr. Philipp Tomsich, Philipp Sehner |

|                | Date/Signature: | 16.02.2018                          |

|                | Approved by:    | Jürgen Meier                        |

|                | Date/Signature: | 16.02.2018                          |

|                |                 |                                     |

## Fujitsu Technology Solutions GmbH Bürgermeister-Ulrich-Str. 100 86199 Augsburg

# History

| Date       | Version | Description                           | Autor                           |

|------------|---------|---------------------------------------|---------------------------------|

| 19.06.2014 | 1.00    | Creation                              | Jürgen Meier<br>Ales Diessner   |

| 27.07.2017 | 1.01    | Added BSI certification ID            | Ales Diessner                   |

| 16.02.2018 | 1.10    | Minor changes after commenting by BSI | Philipp Sehner<br>Ales Diessner |

### © Copyright -2018 – All rights reserved

The information, knowledge and presentations contained in this documentation are property of Fujitsu. The documentation or information contained, knowledge and presentations must not be made accessible to others, published or distributed in any other way, neither completely nor partly, directly nor indirectly, without the permission in writing of Fujitsu.

### Table of Contents

| 1.  | ST-Introduction (ASE_INT)                                                                         | 5  |

|-----|---------------------------------------------------------------------------------------------------|----|

| 1.1 | 1 ST reference and TOE reference                                                                  | 5  |

| 1.2 |                                                                                                   |    |

|     | <ul><li>1.2.1 TOE major security features for operational use</li><li>1.2.2 TOE Type</li></ul>    |    |

|     | 1.2.3 Required non-TOE hardware/software/firmware                                                 |    |

| 1.: | 3 TOE Description                                                                                 | 8  |

| 2.  | ASE_CCL Conformance Claim                                                                         | 9  |

| 2.1 | 1 Common Criteria Conformance Claim                                                               | 9  |

| 2.2 | 2 PP Claim                                                                                        | 10 |

| 2.3 | 3 Package Claim                                                                                   | 10 |

| 3.  | ASE_SPD – Security Problem Definition                                                             | 11 |

| 3.1 | 1 Assumptions                                                                                     | 11 |

| 3.2 | 2 Assets                                                                                          | 12 |

| 3.3 | 3 Subjects                                                                                        | 12 |

| 3.4 | 4 Threats                                                                                         | 12 |

| 3.  | 5 Organizational Security Policy                                                                  | 13 |

| 4.  | ASE_OBJ.1 – Security Objectives                                                                   | 14 |

| 4.1 | 1 Security Objectives for the TOE                                                                 | 14 |

| 4.2 | 2 Security Objectives for the Environment                                                         | 14 |

| 4.: |                                                                                                   |    |

|     | 4.3.1 Countering the threats                                                                      |    |

|     | 4.3.2 Covering the assumptions                                                                    |    |

|     | ASE_ECD – Extended Component Definition                                                           |    |

| 5.′ | 1 Definition of the Family FPT_EMS<br>5.1.1 FPT_EMS TOE emanation                                 |    |

| 6.  | ASE REQ – Security Requirements                                                                   |    |

| 6.1 |                                                                                                   |    |

|     | 6.1.1 User Data Protection (FDP)                                                                  | 19 |

|     | <ul><li>6.1.2 FIA Identification and Authentication</li><li>6.1.3 FTA TOE access</li></ul>        |    |

|     | 6.1.4 Protection of the TSF (FPT)                                                                 |    |

| 6.2 | 2 Security Assurance Requirements for the TOE                                                     | 22 |

| 6.3 |                                                                                                   | 22 |

|     | 6.3.1 Security Functional Requirements Rationale                                                  |    |

|     | <ul><li>6.3.2 Dependency Rationale</li><li>6.3.3 Justification for missing dependencies</li></ul> |    |

|     | 6.3.4 Security Assurance Requirements Rationale                                                   |    |

| 7.  | ASE_TSS – TOE Summary Specification                                                               | 25 |

| 7.  |                                                                                                   |    |

| 7.2 | 2 TOE Security Measures (SM.1)                                                                    | 26 |

| 8.  | Rationales                                                                                        | 27 |

| 8.′ |                                                                                                   |    |

|     | 8.1.1 Security functions and security requirements                                                | 27 |

|     | ©Euiiteu                                                                                          |    |

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 3 of 30 |

| KB100 SCR eSIG | Security Target for KB100 SCR eSIG | Version 1.10, Final |

|----------------|------------------------------------|---------------------|

|                |                                    |                     |

|    | 8.1. | .2 Security functional requirements and security measures | 28 |

|----|------|-----------------------------------------------------------|----|

| 9. | Anı  | nex                                                       | 29 |

|    | 9.1  | Abbreviations                                             | 29 |

|    | 9.2  | Bibliography                                              | 30 |

|   |           | ©Fujitsu                            |              |

|---|-----------|-------------------------------------|--------------|

| 1 | 6.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 4 of 30 |

## 1. ST-Introduction (ASE\_INT)

## **1.1 ST reference and TOE reference**

| Titel:            | Security Target for KB100 SCR eSIG                               |

|-------------------|------------------------------------------------------------------|

| Document Version: | 1.10                                                             |

| Date:             | 16.02.2018                                                       |

| Dok. ID           | ASE_KB100SCReSIG                                                 |

| File name:        | ASE_Fujitsu-KB100SCReSIG-V1.10.docx                              |

| Author(s):        | Dr. Philipp Tomsich, Philipp Sehner, Jürgen Meier, Ales Diessner |

| Zert. ID:         | BSI-DSZ-CC-1046                                                  |

The security features outline the functional and organizational security requirements and procedures for the TOE and its operational environment which meet the security objectives "Secure PIN Entry".

The Target of Evaluation (TOE) is the smartcard keyboard of the KB100 SCR eSIG series with firmware version 2.0.0 and the product index HOS: 01.

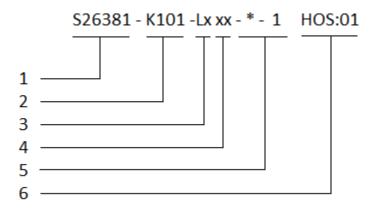

The target of evaluation is divided into the following product variants:

- S26381-K101-L420-\*-1 HOS: 01

- S26381-K101-L120-\*-1 HOS: 01

All product variants contain the same firmware to be evaluated.

Theobroma Systems Design and Consulting GmbH designed the firmware for the S26381-K101-Lx xx-\*-1 HOS:01 smartcard keyboard. The driver software is created by HID Global. Cherry GmbH is the manufacturer, Fujitsu is the product owner and distributor of the TOE.

Figure 1: KB100 SCR eSIG

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 5 of 30 |

| KB100 SCR eSIG | Security Target for KB100 SCR eSIG | Version 1.10, Final |

|----------------|------------------------------------|---------------------|

#### Part number overview

The Product name KB100 SCR eSIG covers the part numbers S26381-K101-Lx xx-\*-1. Below is a brief description of the part number.

The part number is printed at the bottom side of the TOE and is followed by the product index of the TOE.

- 1 = Fujitsu Technology Solutions, reference code group for keyboards and chip card readers

- 2 = Product family (technology, housing form, interface) chip card reader keyboard K101 = certified

- 3 = Housing color (1 = marble grey; 4 = black)

- 4 = Country variant (20 = D)

- 5 = Packaging (-\*-1 = in PE-Bag)

- 6 = Hardware version number (overall version of hardware)

### 1.2 TOE Overview

### **1.2.1 TOE major security features for operational use**

The TOE ensures the functionality for entering a PIN securely.

The keyboard can be used universally in any smartcard-based applications. Possible applications include:

- Qualified digital signature

- Home banking (HBCI)

- Access control (PC login)

When using the TOE as part of a signature application component for "qualified electronic signature", the security functionality of the TOE always works effectively irrespective of the application program running it. For secure PIN entry, only the relevant CT command according to [CCID] needs to be used. The used smartcard must be [ISO 7816] and [EMV2000] compliant processor smartcard. For more details about the supported interfaces and protocols of smartcards, see Chapter 1.3.

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 6 of 30 |

| KB100 SCR eSIG | Security Target for KB100 SCR eSIG | Version 1.10, Final |

|----------------|------------------------------------|---------------------|

|----------------|------------------------------------|---------------------|

### 1.2.2 TOE Type

The TOE is the smartcard keyboard KB100 SCR eSIG with an integrated Class 2 card reader for use in a non-public environment as defined for assumption AE.1 (Chap. 3.1). The physical boundary of TOE is defined by:

- the hardware

- the keyboard's sealed housing

- the USB interface

- the smartcard interface

- Secure PIN- Entry State LED

The logical boundary covers:

- the firmware of the µC

The Quick Start Guide [A26381-K101-Z310-1-8N19], the detailed Operating Instruction [A26381-K101-Z320-1-8N19] and the Software Developer's Guide [SWdevG] are supplied to the user in electronic form.

These documents are available from the Fujitsu Support website. The integrity of the documents is protected using SHA-256 checksum as stated hereinafter:

#### SHA-256 for the Quick Start Guide [A26381-K101-Z310-1-8N19]:

51746651DD6E1BD8DBC7E86B87996BDC5EE797FD53E8AEED53286CD9606F1201

### SHA-256 for the Operating Instruction [A26381-K101-Z320-1-8N19]:

3D79754C06BB4C028EB6D7F4B06308773CE0126EC383BFB2534F29F4C82AE71F

### SHA-256 for the Software Developers Guide [SWdevG]:

32F3717FA7C15F6D69BA8025E8B066840030563F401265C6652CE5E323B8C3AB

### 1.2.3 Required non-TOE hardware/software/firmware

The KB100 SCR eSIG smartcard keyboard has no functionality that works without connecting to a host PC. The keyboard must be connected to a PC. A PC is required with a [USB] standard interface for this. The driver and tools included in the scope of delivery are not part of the TOE.

The following operating systems are supported by the drivers. The operating systems listed are exemplary and not necessarily complete, as fundamentally not required for the secure operation of the TOE.

- Windows 7

- Windows 8 / 8.1

- Windows 10

- Linux

To use the TOE as a secure PIN entry device a corresponding application, e.g. home banking software, is required which use the [CT-API]- or [PC/SC]- Interface of the operating system to set the TOE into the secure PIN entry mode.

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 7 of 30 |

### **1.3 TOE Description**

The TOE, the smartcard keyboard KB100 SCR eSIG, features a keyboard with an integrated Class 2 reader that is able to read processor smartcards in line with [ISO 7816] and [EMV 2000] via various application interfaces ([CT-API], [PC/SC] etc.). The keyboard works with all smartcard data transfer protocols according to [ISO 7816] (T=0, T=1). It also supports data transfer protocols for memory smartcards (2-wire, 3-wire protocols).

The smartcard keyboard recognizes the commands for PIN entry transmitted by the host software and inserts the alphanumeric characters (including small letters, capital letters, numbers and special letters) entered as the PIN to the locations occupied by the command on the smartcard. In this process, only the fact that one of the numerical or alphanumerical keys has been pressed is reported to the host. This enables the host application to show the user that he has pressed a key and how many of the PIN digits have been entered so far. The PIN itself never leaves the smartcard keyboard in plain text.

Secure PIN entry mode is signaled to the user by a red LED. The LEDs for indicating the smartcard status are routed up through a light guide to the casing surface.

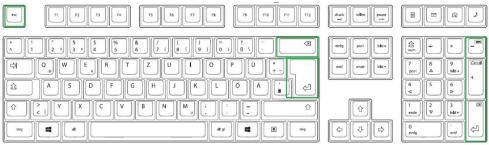

The following table lists the functions and keys which can be used to processing or confirming a PIN during the secure PIN entry mode.

| Function       | Keypad  |                         | Alphanumerical field |

|----------------|---------|-------------------------|----------------------|

|                | Кеу     | Detailed<br>description |                      |

| Confirms entry | [Enter] | [OK]                    | [4]                  |

| Cancel         | [+]     | [CANCEL]                | [ESC]                |

| Undo           | [-]     | [←]                     | [←]                  |

Table 1: Key configuration

Figure 2: Keys for processing or confirming a PIN

The described Secure PIN entry mode is realized by the implemented security function *SF.1 secure PIN entry*, which is supported by the security function *SF.2 memory reprocessing*. This security function ensures that the memory where the entered PIN is stored temporarily will be reprocessed immediately after usage.

The smartcard keyboard can be used on all host systems that have a corresponding USB interface. Power is supplied via the USB bus.

The CT-API and PC/SC application interfaces can be used for all types of smartcard and is provided by the host-PC. All functionalities at the interfaces are mapped in accordance with the [CT-API] and [PC/SC] specification.

The scope of delivery includes:

- Keyboard with attached USB cable

- Quick Start Guide [A26381-K101-Z310-1-8N19] with instructions for installation via Fujitsu website

- Detailed Operating Instruction [A26381-K101-Z320-1-8N19] with instruction for secure use of the product via Fujitsu website

- Software Developer's Guide [SWdevG] via Fujitsu website

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 8 of 30 |

• Driver and software tools via Fujitsu website

Optionally, the software and user guidance [A26381-K101-Z310-1-8N19] and [A26381-K101-Z320-1-8N19] provided via Fujitsu website can also be enclosed on CD with the delivery. But as described under Chapter 1.2.2 "*TOE Type*" only the SHA-256 secured version distributed via Fujitsu website is valid under Common Criteria aspects and part of the certification.

The interface between host and keyboard is based on the functional scope of the [CCID]. The USB interface represents the physical and logical boundary between the TOE and the host system.

The primary aim is to use the smart card keyboard for "qualified digital signature" applications as a secure PIN entry- device.

Since, as a Class 2 reader, the smartcard keyboard is also able to capture identification data (PIN) and securely transmit this data to secure signature creation devices (signature smartcards) it can also be used for applications conforming to the Regulation (EU) No. 910/2014 of the European Parliament and the Council on electronic identification and trust services for electronic transactions [eIDAS]. Furthermore, it transmits the hash value from the application to the signature card and loops back the signature from the card to the signature application.

The following list of supported instruction bytes for secure PIN entry are to be used by the applications and to be supported by the smartcards according to specifications or declined when not supported with an appropriate error message:

| • | VERIFY (ISO/IEC 7816-4):                           | INS=0x20 |

|---|----------------------------------------------------|----------|

| • | CHANGE REFERENCE DATA (ISO/IEC 7816-8):            | INS=0x24 |

| ٠ | DISABLE VERIFICATION REQUIREMENT (ISO/IEC 7816-8): | INS=0x26 |

| • | ENABLE VERIFICATION REQUIREMENT (ISO/IEC 7816-8):  | INS=0x28 |

| ٠ | UNBLOCK APPLICATION (EMV 2000):                    | INS=0x18 |

| • | RESET RETRY COUNTER (ISO/IEC 7816-8):              | INS=0x2C |

|   |                                                    |          |

The housing is sealed with tamper-proof security labels, which self-destruct if removed. The arrangement of the seals and the TOE housing design makes unauthorized opening impossible without breaking a seal.

This allows the user to check the integrity of the keyboard, which he is also prompted to do. Security components and data lines are arranged inside the housing in such a way that it is not possible to gain access through existing openings, e.g. the card slot.

Due to the fact, that the Common Criteria component ALC\_DEL.1 is not part of the certification, the security review ends with the packaging process at the production line. The delivery of the TOE to the secure environment in which the TOE will be used must be negotiated individually with every single customer. Direct delivery to the user or administrator is preferred.

## 2. ASE\_CCL Conformance Claim

### 2.1 Common Criteria Conformance Claim

This Security Target and the TOE claim conformance to

- Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and General Model, CCMB-2012-09-001, Version 3.1, Revision 4, September 2012 [1]

- Common Criteria for Information Technology Security Evaluation, Part 2: Security Functional Components; CCMB-2012-09-002, Version 3.1, Revision 4, September 2012 [2]

- Common Criteria for Information Technology Security Evaluation, Part 3: Security Assurance Requirements; CCMB-2012-09-003, Version 3.1, Revision 4, September 2012 [3]

|            | ©Fujitsu                            |              |

|------------|-------------------------------------|--------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 9 of 30 |

Conformance is claimed for Part 2 extended and Part 3 conformant.

### 2.2 PP Claim

This Security Target claims no Protection Profile.

### 2.3 Package Claim

The following components claimed for the TOE:

ASE\_CCL.1, ASE\_ECD.1, ASE\_INT.1, ASE\_OBJ.2, ASE\_REQ.2, ASE\_SPD.1, ASE\_TSS.1, ADV\_ARC.1, ADV\_FSP.4, ADV\_IMP.1, ADV\_TDS.3, AGD\_OPE.1, AGD\_PRE.1, ALC\_CMC.3, ALC\_CMS.3, ALC\_DVS.1, ALC\_LCD.1, ALC\_TAT.1 ATE\_COV.2, ATE\_DPT.1, ATE\_FUN.1, ATE\_IND.2, AVA\_VAN.3

This component claim corresponds to the assurance level EAL 3 augmented by the components ADV\_FSP.4, ADV\_IMP.1, ADV\_TDS.3, ALC\_TAT.1 and AVA.VAN.3 and reduced by the component ALC\_DEL.1.

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 10 of 30 |

## 3. ASE\_SPD – Security Problem Definition

The following section features the security environment in which the TOE should be used. This covers the security aspects of the environment and the anticipated use of the TOE.

In this context, the assets to be protected and the people involved are explained with respect to the proper use and misuse of the TOE.

The PIN as the identification feature of the smartcard owner, as well as the firmware and hardware of the TOE, must be protected.

Exposing the identification data and security related changes to the TOE are considered to be threats to the TOE by an attacker.

To counteract these threats, mechanisms have been integrated:

- Secure PIN entry is shown by a LED

- Residual information protection by zeroization of memory areas containing sensitive data

- The TOE may only transmit the PIN to the smartcard

- The PIN may only be forwarded to the smartcard via the approved PIN commands

- The TOE is protected by the seal

- The end user is informed of his responsibility using the TOE as PIN entry device.

## 3.1 Assumptions

In general, it is assumed that the end user is informed about his responsibility while using the TOE. The following assumptions show in detail the responsibilities of the user about a secure use of the TOE.

Assumptions regarding the physical conditions

| Assumptions | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE.1        | It is assumed that the TOE is used as a smartcard keyboard for the non-public<br>environment only with single and multi-user PCs in the private domain and in the office<br>environment.<br>Any area which is not accessible for the general public is classed as a non-public<br>environment.<br>Such a non-public environment shall ensure that an attacker cannot install or use any<br>equipment to spy on the entered PIN by the use of audio or video recording equipment<br>or at least it enables the user to identify such equipment.<br>Visitors have only controlled access and visitor policies ensure that they don't carry any<br>equipment for audio or video recording.<br>The access of service providers and external employees to the premises is |

|             | contractually regulated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Assumptions regarding the personnel conditions

| Assumptions | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE.2        | It is assumed that the user is convinced of the integrity of the seal before using for the first time, and periodically thereafter, by checking whether any security-related changes to the seals or smartcard keyboard have been made. |

|             |                                                                                                                                                                                                                                         |

| AE.3        | It is assumed that the user is advised on rules regarding secure storage and non-                                                                                                                                                       |

|             | disclosure of the PIN by the issuer of the smartcard.                                                                                                                                                                                   |

|             | This includes that the user ensures that the PIN is entered unobserved.                                                                                                                                                                 |

| AE.4        | It is assumed that the user checks the status of the LED to ensure that the secure PIN entry mode is active, while entering the PIN using the number keypad.                                                                            |

Assumptions regarding the connection options or the connections to other IT systems or products

| Assumptions | Description                                                                             |

|-------------|-----------------------------------------------------------------------------------------|

| AE.5        | It is assumed that only processor smartcards are used which satisfy the [ISO 7816]      |

|             | and [EMV 2000] specifications. The user or organization which procures the              |

|             | smartcards that will be used with the TOE, must ensure, that the smartcards fulfill the |

|             | proposed requirements.                                                                  |

Table 1: Assumptions

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 11 of 30 |

### 3.2 Assets

The following assets must be protected by the TOE and its environment.

| Assets to be | Description                                                                    |

|--------------|--------------------------------------------------------------------------------|

| protected    |                                                                                |

| PIN          | The PIN as identification code of the user represents a personal secret.       |

|              | The user enters the PIN using the numerical and alphanumerical key area of the |

|              | TOE. This is then sent to the smartcard by the TOE.                            |

|              | The TOE must ensure the confidentiality of the PIN.                            |

Table 2: Assets

### 3.3 Subjects

The following subjects are interacting with the TOE:

| Subject    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Attacker   | <ul> <li>A human or a process acting on his behalf, located outside the TOE. The main goal of the attacker is to gain the entered PIN.</li> <li>The attacker could use the following weak points: <ul> <li>the interface between the TOE and the host- PC,</li> <li>the electromagnetic emanation.</li> </ul> </li> <li>Attack attempts can be conducted from outside of the operational environment. The attacker can also try to get physical access to the TOE within the given access possibilities to the operational environment.</li> <li>The attacker has an enhanced-basic attack potential.</li> </ul> |

| User       | A user uses the TOE as a standard computer input device for normal office work<br>and also as security device where secure PIN entry is required for example as<br>part of a signature application component. The user is non-hostile and knows the<br>existing guidance documents of the TOE. The user is responsible for the secure<br>operation of the TOE.                                                                                                                                                                                                                                                   |

| Host-PC    | A host-PC can be any PC which supports USB devices. The TOE can be used<br>as input device with an integrated class 2 card reader with the host-PC. In<br>addition, the host-PC supports an application with the functionality of PIN<br>verification against a signature card where a class 2 card reader is supported for<br>secure PIN entry.                                                                                                                                                                                                                                                                 |

| Smart Card | The user is in possession of the smart card and the corresponding PIN used for e.g. digital signature. The TOE is handling the communication of the smart card in its card slots and an application on the host-PC.                                                                                                                                                                                                                                                                                                                                                                                              |

Table 3: Subjects

### 3.4 Threats

In the following, all threats are considered which are directed against the assets which require specific protection within the TOE or its environment and are relevant for the secure operation of the TOE. The perpetrators of threats are identified and described in terms of attacks and compromised assets.

| Threats                                                      | Description                                                         |                                                                                 |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| T.1                                                          | Spy on the PIN entered on the TOE via the interface the TOE is conn | Spy on the PIN entered on the TOE via the interface the TOE is connected to the |  |  |

|                                                              | host PC. The attack may be performed using a malicious application  | installed on the                                                                |  |  |

|                                                              | host PC.                                                            |                                                                                 |  |  |

|                                                              | Adverse effects: The PIN information entered by the user may be co  | ompromised.                                                                     |  |  |

|                                                              | Threat agent: Attacker                                              |                                                                                 |  |  |

|                                                              | Asset: PIN                                                          |                                                                                 |  |  |

| T.2 Try to provoke PIN entry and obtain the PIN in this way. |                                                                     |                                                                                 |  |  |

|                                                              | Adverse effects: Obtaining the PIN by provoked PIN entry without a  | ctive security                                                                  |  |  |

|                                                              | functions.                                                          |                                                                                 |  |  |

|                                                              | Threat agent: Attacker                                              |                                                                                 |  |  |

|                                                              | ©Fuiitsu                                                            |                                                                                 |  |  |

| 16.02.2018                                                   | ASE_Fujitsu-KB100SCReSIG-V1.10.docx                                 | Page 12 of 30                                                                   |  |  |

| 10.02.2010                                                   |                                                                     | 1 age 12 01 30                                                                  |  |  |

| Threats | Description                                                                                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Asset: PIN                                                                                                                                                                                                                                          |

| Т.3а    | Manipulation of the TOE into its components (hardware and firmware) or replacing the TOE by a manipulated keyboard to determine the PIN.                                                                                                            |

|         | Adverse effects: Obtaining the PIN by manipulation of the hardware or firmware of                                                                                                                                                                   |

|         | the TOE to bypass the implemented security functions.                                                                                                                                                                                               |

|         | Threat agent: Attacker                                                                                                                                                                                                                              |

|         | Asset: PIN                                                                                                                                                                                                                                          |

| T.3b    | Read out the PIN which is stored temporarily in the TOE.                                                                                                                                                                                            |

|         | Adverse effects: Read out the PIN over TOE interfaces or direct after internal                                                                                                                                                                      |

|         | processing.                                                                                                                                                                                                                                         |

|         | Threat agent: Attacker                                                                                                                                                                                                                              |

|         | Asset: PIN                                                                                                                                                                                                                                          |

| T.4     | Writing the PIN in an unprotected area of the smart card to then read it.                                                                                                                                                                           |

|         | Adverse effects: Direct the PIN to unprotected areas of a smart card.                                                                                                                                                                               |

|         | Threat agent: Attacker                                                                                                                                                                                                                              |

|         | Asset: PIN                                                                                                                                                                                                                                          |

| T.5     | Make security-related changes to the TOE by tampering with the security seal.                                                                                                                                                                       |

|         | <b>Adverse effects:</b> Manipulation the TOE by tampering the security seals to obtain the entered PIN.                                                                                                                                             |

|         | Threat agent: Attacker                                                                                                                                                                                                                              |

|         | Asset: PIN                                                                                                                                                                                                                                          |

| Т.6     | Eavesdropping of the electromagnetic emanation to draw conclusion about the entered PIN by analyses of the recorded signals. The attacker and the attack equipment is located outside the operational environmental of the TOE in an adjacent area. |

|         | Adverse effects: Eavesdropping of the PIN with equipment to record<br>electromagnetic emanation for subsequent analysis in order to compromise PIN<br>information from adjacent areas.                                                              |

|         | Threat agent: Attacker                                                                                                                                                                                                                              |

|         | Asset: PIN                                                                                                                                                                                                                                          |

Table 4: Threats

## 3.5 Organizational Security Policy

No organizational security policy is defined.

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 13 of 30 |

## 4. ASE\_OBJ.1 – Security Objectives

The security objectives for the TOE and its environment are defined in this chapter. The following security objectives counteract all identified threats and outline the assumptions.

In chapter 4.1 the security objectives for the TOE are defined, while in chapter 4.2, the security objectives for the environment of the TOE are specified.

Chapter 4.3 presents the correlations between the identified assumptions and threats and the defined security objectives.

## 4.1 Security Objectives for the TOE

The security objectives for the TOE are listed in the following table.

| Security objectives for the TOE | Description                                                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0.1                             | The TOE ensures that the PIN is not stored, except at the time of processing.                                            |

| 0.2                             | The TOE ensures that secure PIN entry mode is clearly signaled to the user.                                              |

| 0.3                             | The TOE ensures that the PIN is only transferred to the smartcard.                                                       |

| 0.4                             | The TOE ensures that the PIN is passed on to the smartcard only by means of PIN command with approved instruction bytes. |

| O.5                             | The TOE ensures that any security changes to the TOE are recognizable by the security seal.                              |

| O.6                             | The TOE ensures that the electromagnetic emanation cannot be used to simply draw conclusion about the entered PIN.       |

Table 5: Security objectives for the TOE

## 4.2 Security Objectives for the Environment

The user is advised on rules regarding secure storage and non-disclosure of the PIN by the issuer of the smart card.

The end user must be informed of his responsibility while using the TOE.

The security objectives for the environment are defined in the following table.

| Security objectives for the environment | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE.1                                    | The TOE must be used as a smartcard keyboard for the non-public<br>environment. This comprises that the user is obligated to check the operational<br>environment regularly about installed audio and video recording equipment used<br>for spy attacks on the PIN.<br>It must be ensured that visitors, service providers or external employees cannot |

|                                         | install or carry any kind of audio or video recording equipment.                                                                                                                                                                                                                                                                                        |

| OE.2                                    | The user must check the integrity of the security seal (seal number) and the TOE regularly before using the device.                                                                                                                                                                                                                                     |

| OE.3                                    | The user must follow the instructions of the card issuer regarding the secure handling of the card and the PIN and ensure that the PIN is entered unobserved.                                                                                                                                                                                           |

| OE.4                                    | While entering the PIN, the user must check the status of the LED to ensure that the secure PIN entry mode is active.                                                                                                                                                                                                                                   |

| OE.5                                    | The user may only use processor cards which satisfy the [ISO 7816] and [EMV 2000] specifications.                                                                                                                                                                                                                                                       |

Table 6: Security objectives for the environment

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 14 of 30 |

## 4.3 Security Objectives Rationale

The following table provides an overview for the security objectives coverage. The following chapters provide a more detailed explanation of this mapping:

|      | 0.1 | O.2 | 0.3 | 0.4 | O.5 | 0.6 | OE.1 | OE.2 | OE.3 | OE.4 | OE.5 |

|------|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| T.1  |     |     | Х   |     |     |     |      |      |      |      |      |

| T.2  |     | Х   |     |     |     |     |      |      |      | Х    |      |

| T.3a |     |     |     |     | Х   |     |      | Х    |      |      |      |

| T.3b | Х   |     |     |     |     |     |      |      |      |      |      |

| T.4  |     |     |     | Х   |     |     |      |      |      |      |      |

| T.5  |     |     |     |     | Х   |     |      |      |      |      |      |

| T.6  |     |     |     |     |     | Х   |      |      |      |      |      |

| AE.1 |     |     |     |     |     |     | Х    |      |      |      |      |

| AE.2 |     |     |     |     |     |     |      | Х    |      |      |      |

| AE.3 |     |     |     |     |     |     |      |      | Х    |      |      |

| AE.4 |     |     |     |     |     |     |      |      |      | Х    |      |

| AE.5 |     |     |     |     |     |     |      |      |      |      | Х    |

Table 7: Security objectives coverage

### 4.3.1 Countering the threats

The threat T.1 describes that an attacker may try to eavesdrop and log the communication between the TOE and the host system by a malicious tool installed on the host system, to obtain an entered PIN or bypass the security functions. This treat is countered by the objective O.3 which describes that the PIN will never leave the TOE other than to the corresponding smartcard.

The threat **T.2**, which describes that an attacker can provoke the PIN entry by a program from outside of the TOE is countered by the objective O.2 and OE.4. O.2 describes that the TOE will signal the secure PIN entry mode clearly to the user and OE.4 ensures that the user check the status of the secure PIN entry LED while he is entering the PIN to be sure that the secure PIN entry mode is active. Threat **T.3a** which describes the manipulation of the TOE into its components (hardware and firmware) to bypass the security functions is countered by the objective O.5 which ensures that manipulation of the TOE is recognizable because of the use of security seals.

It is also assumed, that an attacker can replace the TOE by a manipulated keyboard. The Objective **OE.2** counteracts to this threat, which is an assumption to the operational environment that the serial numbers of the security seals will be checked regularly by the user.

Objective O.1 which ensures that the PIN will never be stored in the TOE, except during the processing counters the threat **T.3b** which describes the reading of the PIN after PIN entry from memories.

The threat **T.4**, which describes that an attacker could try to redirect the PIN to an unprotected area of a smart card, is covered by the objective O.4. This objective ensures that the TOE only accepts PIN commands with permitted instruction bytes.

The threat **T.5**, which describes that an attacker could tamper with the security seal to manipulate the TOE is countered by the objective O.5 which claims that manipulations of the TOE are recognizable because of the use of security seals.

The threat **T.6**, which describes that an attacker can eavesdrop the PIN by analyzing the electromagnetic emanation is countered by the security objective O.6 which claims that the electromagnetic emanation cannot be exploited by a simply way.

### 4.3.2 Covering the assumptions

| ł | AE.1 | It is assumed that the TOE is used as a smartcard keyboard for the non-public environment. |                                                                              |  |  |  |

|---|------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

|   |      | OE.1                                                                                       | The TOE must be used as a smartcard keyboard for the non-public environment. |  |  |  |

|   |      |                                                                                            |                                                                              |  |  |  |

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 15 of 30 |

| KB100 | SCR | eSIG |

|-------|-----|------|

|       |     |      |

Security Target for KB100 SCR eSIG

| AE.2                                                                                                                        | It is assumed that the user is convinced of the integrity of the seal before using for the first time, and periodically thereafter, by checking whether any security-related changes to the smartcard keyboard have been made. |                                                                                                                                                                                               |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                             | OE.2 establish an objective which covers the assumption directly                                                                                                                                                               |                                                                                                                                                                                               |  |  |  |  |  |

| AE.3                                                                                                                        | handling                                                                                                                                                                                                                       | umed that the user follows the instructions of the card issuer regarding the secure<br>of the card and the PIN. Thus, it is also assumed that the user ensures that the PIN is<br>unobserved. |  |  |  |  |  |

|                                                                                                                             | OE.3                                                                                                                                                                                                                           | establish an objective which covers the assumption directly                                                                                                                                   |  |  |  |  |  |

|                                                                                                                             |                                                                                                                                                                                                                                |                                                                                                                                                                                               |  |  |  |  |  |

| <b>AE.4</b> It is assumed that the user checks the status of the LED to ensure that mode is active, while entering the PIN. |                                                                                                                                                                                                                                | umed that the user checks the status of the LED to ensure that the secure PIN entry active, while entering the PIN.                                                                           |  |  |  |  |  |

|                                                                                                                             | OE.4                                                                                                                                                                                                                           | establish an objective which covers the assumption directly                                                                                                                                   |  |  |  |  |  |

|                                                                                                                             |                                                                                                                                                                                                                                |                                                                                                                                                                                               |  |  |  |  |  |

| AE.5                                                                                                                        |                                                                                                                                                                                                                                | umed that only processor smartcards are used which satisfy the [ISO 7816] and [EMV pecifications.                                                                                             |  |  |  |  |  |

|                                                                                                                             | OE.5                                                                                                                                                                                                                           | establish an objective which covers the assumption directly                                                                                                                                   |  |  |  |  |  |

Table 8: Covering the assumptions

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 16 of 30 |

## 5. ASE\_ECD – Extended Component Definition

This Security Target uses components defined as extensions to CC part 2. The defined components are drawn from extended component definition [PP\_0068].

## 5.1 Definition of the Family FPT\_EMS

The family FPT\_EMS (TOE Emanation) of the class FPT (Protection of the TSF) is defined here to describe the IT security functional requirements of the TOE. The TOE shall prevent attacks against secret data processed by the TOE where the attack is based on external observable physical phenomena of the TOE. Examples of such attacks are evaluation of TOE's electromagnetic radiation, timing attacks, etc. This family describes the functional requirements for the limitation of intelligible emanations being not directly addressed by any other component of CC part 2 [CC2]. The family 'TOE Emanation (FPT\_EMS)' is specified as follows:

### 5.1.1 FPT\_EMS TOE emanation

This family defines requirements to mitigate intelligible emanations. Component levelling:

FPT\_EMS.1 TOE emanation has one constituent:

FPT\_EMS.1.1 Limit of Emissions requires to not emit intelligible emissions enabling access to TSF data or user data.

Management: FPT\_EMS.1 There are no management activities foreseen.

Audit: FPT\_EMS.1 There are no actions defined to be auditable.

### FPT\_EMS.1 TOE Emanation

FPT\_EMS.1.1 The TOE shall not emit [assignment: *types of emissions*] in excess of [assignment: *specified limits*] enabling access to [assignment: *list of types of TSF data*] and [assignment: *list of types of user data*].

Hierarchical to: No other components

Dependencies: No dependencies

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 17 of 30 |

## 6. ASE\_REQ – Security Requirements

This Chapter defines the functional requirements and the security assurance requirements for the TOE and its environment.

Operations for assignment, selection, refinement and iteration have been made.

All operations which have been performed from the original text of [CC2] are written in *italics for assignments*, <u>underlined for selections</u> and **bold text for refinements**. Furthermore the [brackets] from [CC2] are kept in the text

### 6.1 Security Functional Requirements for the TOE

The TOE has to satisfy the SFRs delineated in the following table. The  $4^{th}$  row of the table designates the dependencies of the SFRs.

| Nr. | Component | Description                             | Dependencies           |

|-----|-----------|-----------------------------------------|------------------------|

|     | FDP       | User Data Protection                    |                        |

| 1   | FDP_ACC.1 | Subset access control                   | FDP_ACF.1              |

| 2   | FDP_ACF.1 | Security attribute based access control | FDP_ACC.1<br>FMT_MSA.3 |

| 3   | FDP_RIP.1 | Subset residual information protection  | none                   |

|     | FIA       | Identification and authentication       |                        |

| 4   | FIA_UAU.7 | Protected authentication feedback       | FIA_UAU.1              |

|     | FTA       | TOE access                              |                        |

| 5   | FTA_TAB.1 | Default TOE access banners              | none                   |

|     | FPT       | Protection of the TSF                   |                        |

| 6   | FPT_EMS.1 | TOE Emanation                           | none                   |

| 7   | FPT_PHP.1 | Passive detection of physical attack    | none                   |

Table 9: Security functional requirement for the TOE

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 18 of 30 |

### 6.1.1 User Data Protection (FDP)

#### 6.1.1.1 FDP\_ACC.1 Subset access control

**FDP\_ACC.1.1** The TSF shall enforce the [*Smart card reader access control policy*] on

#### L Subjects:

- User via key matrix interface

- Host- PC via USB interface

- Smart card via smart card interface

- Objects:

- PIN

- Secure PIN entry mode LED

Operations among subjects and objects covered by the SFP:

- Entry of the PIN

- Transfer of the PIN

- Control of the secure PIN entry LED

].

Hierarchical to: No other components. Dependencies: FDP\_ACF.1 Security attribute based access control

### 6.1.1.2 FDP\_ACF.1 Security attribute based access control

**FDP\_ACF.1.1** The TSF shall enforce the [*smartcard reader access control policy*] to objects based on the following:

list of subjects:

- User via the key matrix interface

- Host- PC via USB interface

- Smart Card via smart card reader interface attribute: [none]

objects:

- PIN

- Secure PIN entry mode LED

Attribute: State of the Secure PIN entry mode LED

- ].

- **FDP\_ACF.1.2** The TSF shall enforce the following rules to determine if an operation among controlled subjects and controlled objects is allowed:

- l

The Host- PC (subject) sends via the USB- Interface an explicit command from an application to the smart card interface, whereby the secure PIN entry LED (object) will be triggered (operation) by the TOE. The entered PIN (object) will be send (operation) to the corresponding smart card, if the command structure of the command meets [CCID] and the instruction correlates with one of the following instruction bytes:

• VERIFY (ISO/IEC 7816-4)

- INS= 0x20

- CHANGE REFERENCE DATA (ISO/IEC 7816-8) INS=0x24

- DISABLE VERIFICATION REQUIREMENT (ISO/IEC 7816-8) INS=0x26

ENABLE VERIFICATION REQUIREMENT (ISO/IEC 7816-8) INS=0x28

- ENABLE VERIFICATION REQUIREMENT (ISO/IEC 7816-8) INS=0x28

RESET RETRY COUNTER (ISO/IEC 7816-8) INS=0x2C

- RESET RETRY COUNTER (ISO/IEC 7816-8)

INS=0x2C

UNBLOCK APPLICATION (EMV 2000):

INS=0x18

- UNBLUCK AFFLICATION (EIVIV 2000).

- The user (subject) can only enter (operation) the PIN (object) via defined keys of the alphanumeric key area and the numeric pad of the keyboard.

- The TOE sends (operation) the PIN (object) to the smart card (subject) in the smart card interface only.

- ].

©Fujitsu

16.02.2018

ASE\_Fujitsu-KB100SCReSIG-V1.10.docx

Page 19 of 30

| KB100 SCR eSIG    |                                                                                                                                               | Security Target for KB100 SCR eSIG                                                                                                                                                                              | Version 1.10, Final                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| FDP_ACF.1.3       | follow                                                                                                                                        | SF shall explicitly authorize access of subj<br>ing additional rules:<br><i>rther rules required for the TSF</i> ].                                                                                             | jects to objects based on the                                  |

| FDP_ACF.1.4       | The TSF shall explicitly deny access of subjects to objects based on the following additional rules: [No further rules required for the TSF]. |                                                                                                                                                                                                                 |                                                                |

| Hierarchical to:  | No oth                                                                                                                                        | er components.                                                                                                                                                                                                  |                                                                |

| Dependencies:     |                                                                                                                                               | ACC.1 Subset access control<br>MSA.3 Static attribute initialization                                                                                                                                            |                                                                |

| 6.1.1.3 FDP_RIP.1 | Subse                                                                                                                                         | et residual information protection                                                                                                                                                                              |                                                                |

| FDP_RIP.1.1       |                                                                                                                                               | SF shall ensure that any previous informat<br>unavailable upon the <u>[deallocation of the r</u><br>s:<br>[<br>- <i>PIN</i><br>- Secure PIN entry mode LED<br>].                                                |                                                                |

| Application Note  | sm<br>no<br>key<br>FD                                                                                                                         | ter activation, the forwarding of a PIN comp<br>artcard or cancellation, the PIN memory a<br>personal identification data or data fragme<br>yboard.<br>P_RIP1.1 for the PIN LED means that the<br>D is ensured. | rea is zeroized to ensure that<br>ents remain in the smartcard |

Hierarchical to: No other components.

Dependencies: No dependencies.

### 6.1.2 FIA Identification and Authentication

### 6.1.2.1 FIA\_UAU.7 Protected authentication feedback

**FIA\_UAU.7.1** The TSF shall provide only [*non-PIN placeholder character*] to the user while the authentication is in progress.

Hierarchical to: No other components.

Dependencies: FIA\_UAU.1 Timing of authentication

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 20 of 30 |

#### 6.1.3 FTA TOE access

#### 6.1.3.1 FTA\_TAB.1 Default TOE access banners

**FTA\_TAB.1.1** Before establishing a user session, the TSF shall **indicate**, whether the TOE is in a secure state or not.

Application Note 2: The state of secure PIN entry mode will be indicated by a red LED.

Hierarchical to: No other components.

Dependencies: No dependencies.

### 6.1.4 Protection of the TSF (FPT)

### 6.1.4.1 FPT\_EMS.1 TOE Emanation

**FPT\_EMS.1.1** The TOE shall not emit [information about the timing of the matrix scan during secure PIN entry] in excess of [non-useful information] enabling access to [none] and [PIN].

Application Note 3: The key matrix scan during the secure PIN entry mode must be scrambled. Therefore, a random number generator must be used to scramble the scan randomly.

The random number as seed for the random number generator must be loaded into the TOE securely.

It must be ensured during the preparative installation procedure of the TOE at production site that a random number from sufficient quality is been used. Evidences have been taken within the scope of the ALC evaluation.

#### 6.1.4.2 FPT\_PHP.1 Passive detection of physical attack

- **FPT\_PHP.1.1** The TSF shall provide unambiguous detection of physical tampering that might compromise the TSF.

- Application Note 4: Based on authentic and tamper-proof security seals affixed over the join between the bottom and top parts of the housing is it possible to reliably establish that the hardware has not been tampered with.

- **FPT\_PHP.1.2** The TSF shall provide the capability to determine whether physical tampering with the TSF's devices or TSF's elements has occurred.

- Application Note 5: This can be ensured because the housing cannot be opened without breaking the seal. The nature (destruction characteristics) of the seal ensures that it cannot be removed and re-attached without damaging it.

Hierarchical to: No other components.

Dependencies: No dependencies.

|            | ©Fujitsu                            |               |

|------------|-------------------------------------|---------------|

| 16.02.2018 | ASE_Fujitsu-KB100SCReSIG-V1.10.docx | Page 21 of 30 |

### 6.2 Security Assurance Requirements for the TOE

The TOE fulfills the below listed Security Assurance Requirements which represents EAL 3 augmented by the components marked in bold text and reduced by the component ALC\_DEL.1. The complete text for these requirements can be found in Part 3 of the Common Criteria [CC3].

| Assurance Class         | Assurance Components                                |

|-------------------------|-----------------------------------------------------|

| ADV: Development        | ADV_ARC.1: Security architecture description        |

|                         | ADV_FSP.4 Complete functional specification         |

|                         | ADV_IMP.1 Implementation representation of the TSF  |

|                         | ADV_TDS.3 Basic modular design                      |

| AGD: Guidance documents | AGD_OPE.1 Operational user guidance                 |

|                         | AGD_PRE.1 Preparative procedure                     |

| ALC: Life-cycle support | ALC_CMC.3 Authorisation control                     |

|                         | ALC_CMS.3 Implementation representation CM coverage |

|                         | ALC_DVS.1 Identification of security measures       |

|                         | ALC_LCD.1 Developer defined life-cycle model        |

|                         | ALC_TAT.1 Well-defined development tools            |

|                         | ASE_CCL.1 Conformance claims                        |

| ASE: Security Target    | ASE_ECD.1 Extended components definition            |

| evaluation              | ASE_INT.1 ST Introduction                           |

|                         | ASE_OBJ.2 Security objectives                       |

|                         | ASE_REQ.2 Derived security requirements             |

|                         | ASE_SPD.1 Security problem definition               |

|                         | ASE_TSS.1 TOE summary specification                 |

|                         | ATE_COV.2 Analysis of coverage                      |

| ATE: Tests              | ATE_DPT.1 Testing: basic design                     |

|                         | ATE_FUN.1 Functional testing                        |

|                         | ATE_IND.2 Independent testing – sample              |

| AVA: Vulnerability      | AVA_VAN.3 Vulnerability analysis                    |

| assessment              |                                                     |

Table 10: Chosen Evaluation Assurance Requirements

## 6.3 Security Requirements Rationale

### 6.3.1 Security Functional Requirements Rationale

The following table provides an overview for security functional requirements coverage.

|           | 0.1 | 0.2 | 0.3 | 0.4 | O.5 | 0.6 |

|-----------|-----|-----|-----|-----|-----|-----|

| FDP_ACC.1 |     |     | Х   | X   |     |     |

| FDP_ACF.1 |     |     | X   | X   |     |     |